# An Improved PWM Strategy for Z-Source Inverter With Maximum Boost Capability and Minimum Switching Frequency

Yan Zhang<sup>®</sup>, *Member, IEEE*, Jinjun Liu<sup>®</sup>, *Senior Member, IEEE*, Xinying Li, *Student Member, IEEE*, Xiaolong Ma, Sizhan Zhou<sup>®</sup>, *Student Member, IEEE*, Hongliang Wang<sup>®</sup>, *Senior Member, IEEE*, and Yan-Fei Liu, *Fellow, IEEE*

Abstract—Z-source inverter provides a competitive single-stage dc-ac power conversion with the capability of both buck and boost voltage regulation. In order to maximize voltage gain and to increase efficiency, this paper proposes an improved pulse-width modulation (PWM) strategy. By adjusting the shoot-through duty ratio of one-phase leg, it regulates the average value of intermediate dc-link voltage, which is the same as the instantaneous maximum of three-phase line voltage in one switching time period  $(T_s)$ . And the other two-phase legs maintain the fixed switching states. Thus, the equivalent switching frequency of power devices in the inverter bridge is reduced to  $1/3f_s$  ( $f_s$  is the frequency corresponding to  $T_s$ ). The operating principles and closed-loop controller design are analyzed and verified by simulation and experiments. Compared with the existing PWM strategies, the improved PWM (IPWM) strategy demonstrates higher efficiency under full operation range of low voltage gain (1.27-2) application. However, with the IPWM strategy, the inductor current and capacitor voltage contain sixtime-line-frequency ripples, which consequently require large size of the passive components when the output frequency is very low. Thus, it is also suitable for 400-800-Hz medium frequency aircraft and vessel power supply system due to a relatively high output line frequency. Furthermore, the idea of IPWM strategy can be extended to other kinds of three-phase impedance network-based inverters.

*Index Terms*—Closed-loop control, dc/ac conversion, minimum switching frequency, pulse-width modulation (PWM) strategy, voltage gain, Z-source inverter.

# I. INTRODUCTION

ONVENTIONAL two-level three-phase voltage source inverter (VSI) can only perform buck voltage regulation.

Manuscript received May 27, 2016; revised December 14, 2016; accepted January 22, 2017. Date of publication January 30, 2017; date of current version October 6, 2017. This work was supported in part by the State Key Laboratory of Electrical Insulation and Power Equipment under Grant EIPE16310 and in part by the Power Electronics Science and Education Development Program of Delta Environmental and Educational Foundation under Grant DREG2016010. Recommended for publication by Associate Editor Dr. D. Vinnikov.

Y. Zhang, J. Liu, X. Li, X. Ma, and S. Zhou are with the State Key Lab of Electrical Insulation and Power Equipment, School of Electrical Engineering, Xi'an Jiaotong University, Xi'an 710049, China (e-mail: zhangyanjtu@163.com; jjllu@mail.xjtu.edu.cn).

H. Wang and Y.-F. Liu are with the Department of Electrical and Computer Engineering, Queen's University, Kingston, ON K7L 3N6, Canada (e-mail: hongliang.wang@queensu.ca; yanfei.liu@queensu.ca).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2017.2661321

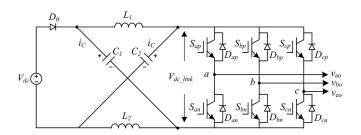

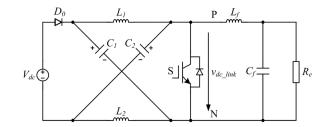

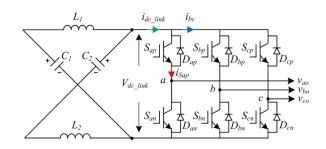

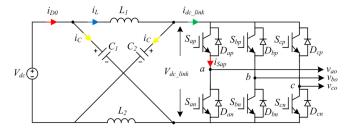

Fig. 1. Z-source inverter.

For applications requiring both buck and boost power conversion, an additional boost dc-dc converter is required in the front. In view of two-stage power conversion increasing system cost and lowering efficiency, Peng [3] proposed Z-source inverter, shown in Fig. 1, introducing a unique impedance network between the source and the inverter bridge. It achieves voltage boost capability by advantageously adopting shoot through (ST) of inverter-bridge legs, which provides a potential lowcost, high-efficiency, and single-stage power conversion when the boost ratio is low (1–2) [33]. Furthermore, the ST permission of inverter-bridge legs and elimination of dead-zone time are beneficial to improve the system reliability and quality of output waveforms. Since Z-source inverter overcomes the limitations of traditional VSI, various new topologies [4]-[14], pulse-width modulation (PWM) strategies [15]-[26], and model and control methods [27]-[31] were proposed to improve its performance.

The existing widely used PWM strategies for Z-source inverter include simple constant boost control (SCPWM) [3], maximum boost control (MPWM) [16], and maximum constant boost control (MCPWM) [17], according to the intermediate dc-link voltage utilization. SCPWM uses carrier wave based sinusoidal pulse width modulation (SPWM), and it has the drawback of insufficient dc-link voltage utilization. In order to increase voltage gain as well as to reduce voltage stress of switching devices, Peng *et al.* [16] proposed MPWM, which utilizes all the zero states for ST interval. However, the periodic ST interval causes the six-time-line-frequency ( $6\omega$ ) ripples in the dc-side impedance network. In order to alleviate the undesired influence of low-frequency ripples, Shen *et al.* [17] proposed MCPWM with fixed ST interval. According to the distribution

0885-8993 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

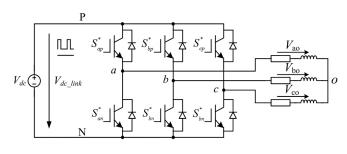

Fig. 2. Three-phase VSI.

of ST current in three-phase legs, there are two major categories: single-phase leg ST (1P ST) and three-phase leg ST (3P ST) [19], [20]. 1P ST method inserts ST interval by overlapping the upper and lower switches in each phase leg at every switching commutation. Thus, the ST interval is averagely divided into six parts in one switching time period ( $T_s$ ), which is beneficial to reduce the volume of inductors considerably. 3P ST method inserts ST interval in three-phase legs simultaneously, which is beneficial to reduce the current stress and conduction loss of power devices. However, it introduces an additional switching commutation.

This paper starts by reviewing typical PWM strategies of Z-source inverter through modification of the conventional VSI PWM strategies [e.g., SPWM and space vector modulation (SVM)] in Section II, and then proposes an improved PWM (IPWM) strategy with maximum voltage gain and minimum switching frequency in Section III. By adjusting the ST duty ratio of one phase leg, it regulates the average value of intermediate dc-link voltage, which is the same as the instantaneous maximum of three-phase line voltage in one switching time period  $(T_s)$ . As a result, the equivalent switching frequency of power devices in the inverter bridge is reduced to  $1/3f_s$  ( $f_s = 1/T_s$ ), which makes a great contribution to the reduction of switching losses. After that, a comprehensive comparison between the IPWM strategy and existing PWM strategies is carried out in terms of power device and passive component requirements in Section IV. The detailed closed-loop controller design is investigated in Section V. Simulation and experiment verification are presented in Section VI. The conclusion of this study is outlined in Section VII.

## II. TYPICAL PWM STRATEGIES OF Z-SOURCE INVERTER

The aforementioned PWM strategies including SCPWM, MPWM, and MCPWM can use either 1P ST or 3P ST. They are referred as SCPWM + 1P ST, SCPWM + 3P ST, MCPWM + 1P ST, MCPWM + 3P ST, MPWM + 1P ST, and MPWM + 3P ST in this study. Usually, all these six typical PWM strategies can be derived by modifying the modulation waveforms of conventional three-phase VSI.

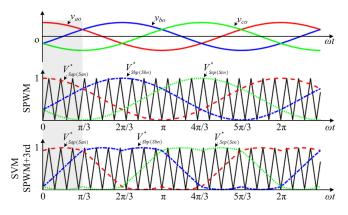

Figs. 2 and 3 show the main circuit of conventional threephase VSI and three typical PWM strategies including SPWM, SPWM with 3rd harmonic injection (SPWM + 3rd) or SVM. Three-phase symmetrical output voltage and output power can

Fig. 3. Equivalent modulation waveforms of carrier wave-based SPWM and SVM.

be expressed as follows:

$$\begin{cases} v_{\rm ao}(\omega t) = \hat{v}_{\rm ac} \cdot \cos(\omega t) \\ v_{\rm bo}(\omega t) = \hat{v}_{\rm ac} \cdot \cos\left(\omega t - \frac{2}{3}\pi\right) \\ v_{\rm co}(\omega t) = \hat{v}_{\rm ac} \cdot \cos\left(\omega t + \frac{2}{3}\pi\right) \end{cases}$$

(1)

$$P_o = \frac{3}{2} \cdot \hat{v}_{\rm ac} \cdot \hat{i}_{\rm ac} \cos(\varphi)$$

(2)

where  $\hat{v}_{\rm ac}$  and  $\hat{i}_{\rm ac}$  are the peak value of phase voltage and current,  $\cos(\varphi)$  is the load power factor,  $\omega = 2\pi f_{\rm line}$ , and  $f_{\rm line}$  is the fundamental frequency of output phase voltage.

The voltage gain, as well as modulation index, is defined as  $\hat{v}_{ac}$  over half of dc-link voltage

$$M_i = \frac{\hat{v}_{\rm ac}}{v_{\rm dc}/2}.$$

(3)

As is shown in Fig. 3, based on the assumption that the amplitude of triangular waveform is normalized, the expressions of three-phase modulation waveforms for SPWM and SVM (in the first sextant) are expressed as (4) and (5), respectively. Compared with SPWM, SVM can increase the Modulation index to  $2/\sqrt{3}$

$$\begin{cases} V_{\text{Sap(San)}}^{*}(\omega t) = \frac{1}{2} + \frac{M_{i}}{2} \cdot \cos(\omega t) \\ V_{\text{Sbp(Sbn)}}^{*}(\omega t) = \frac{1}{2} + \frac{M_{i}}{2} \cdot \cos\left(\omega t - \frac{2}{3}\pi\right) & \text{For SPWM} \\ V_{\text{Scp(Scn)}}^{*}(\omega t) = \frac{1}{2} + \frac{M_{i}}{2} \cdot \cos\left(\omega t + \frac{2}{3}\pi\right) \end{cases}$$

(4)

where  $0 \leq M_i \leq 1, 0 \leq \omega t \leq 2\pi$ .

$$\begin{cases} V_{\text{Sap}(\text{San})}^{*}(\omega t) = \frac{1}{2} + \frac{\sqrt{3}M_{i}}{4} \cdot \cos\left(\omega t - \frac{\pi}{6}\right) \\ V_{\text{Sbp}(\text{Sbn})}^{*}(\omega t) = \frac{1}{2} - \frac{3M_{i}}{4} \cdot \cos\left(\omega t + \frac{\pi}{3}\right) & \text{For SVM} \\ V_{\text{Scp}(\text{Scn})}^{*}(\omega t) = \frac{1}{2} - \frac{\sqrt{3}M_{i}}{4} \cdot \cos\left(\omega t - \frac{\pi}{6}\right) \\ \text{where } 0 \le M_{i} \le \frac{2}{\sqrt{3}}, 0 \le \omega t \le \frac{\pi}{3}. \end{cases}$$

(5)

607

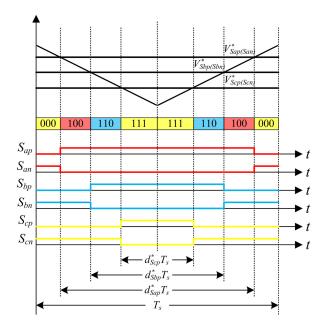

Fig. 4. Switching states of SPWM or SVM in the first sextant  $(0 \le \omega t \le \pi/3)$ .

Fig. 4 shows the switching state of SPWM or SVM in the first sextant. The comparison results of modulation waveforms and triangular wave are adopted to control the switching state of the upper and lower switches in each phase. Thus, the on-state duty ratio of upper and lower switches are  $d_{\text{Sip}}^*(\omega t) = V_{\text{Sip}}^*(\omega t)$  and  $d_{\text{Sin}}^*(\omega t) = 1 - V_{\text{Sip}}^*(\omega t)$  (*i* represents *a*, *b*, or *c*).

As described in Peng [3], voltage gain of Z-source inverter is defined as the ratio of the peak phase voltage  $\hat{v}_{ac}$  over half of dc source voltage

$$G = \frac{\hat{v}_{\rm ac}}{V_{\rm dc}/2} = B \cdot M_i \tag{6}$$

in which

$$B = \frac{1}{1 - 2d_{\rm ST}} \tag{7}$$

where  $M_i$  is the modulation index, and B is the boost factor determined by ST duty ratio  $d_{ST}$ .

The obtainable  $d_{ST}$  increases with the decrease of  $M_i$ . As described by Shen *et al.* [17],  $d_{ST}$  and  $M_i$  meet

$$d_{\rm ST} = 1 - M_i \quad (0 \le M_i \le 1) \quad \text{for SCPWM} \tag{8}$$

$$d_{\rm ST} = 1 - \frac{\sqrt{3}}{2} M_i \quad (0 \le M_i \le \frac{2}{\sqrt{3}}) \text{ for MCPWM } (9)$$

$$d_{\rm ST}(\omega t) = 1 - \frac{\sqrt{3}}{2} M_i \cos\left(\omega t - \frac{\pi}{6}\right) \quad \left(0 \le \omega t \le \frac{\pi}{3}, \\ 0 \le M_i \le \frac{2}{\sqrt{3}}\right) \quad \text{for MPWM.}$$

(10)

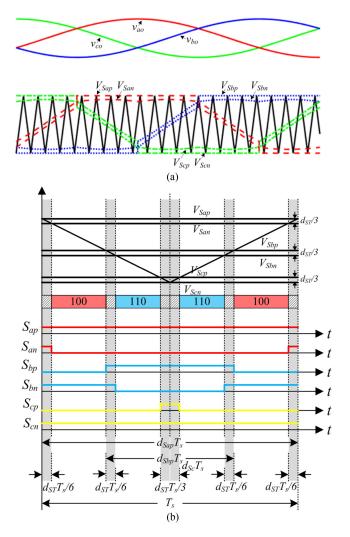

# A. SCPWM + 1P ST and MCPWM + 1P ST

Fig. 5 shows the equivalent carrier wave based PWM and the switching state for MCPWM + 1P ST. The ST interval is divided into six parts and averagely inserted in each phase by overlapping the upper and lower switches at every switching commutation. The control reference of six switches for Z-source

Fig. 5. MCPWM with 1P ST (MCPWM + 1P ST). (a) Equivalent carrier wave based PWM. (b) Switching states in the first sextant  $(0 \le \omega t \le \pi/3)$ .

inverter can be obtained as (11) by shifting the modulation waveforms of conventional three-phase VSI [19].  $V_{\text{max}}^*$ ,  $V_{\text{mid}}^*$ , and  $V_{\text{min}}^*$  refer to the modulation waveform of conventional three-phase VSI. Take the first sextant, for example, the output voltage meets  $v_{ao} > v_{bo} > v_{co}$ , so  $V_{\text{max}}^* = V_{\text{Sap}(\text{San})}^*$ ,  $V_{\text{mid}}^* = V_{\text{Sbp}(\text{Sbn})}^*$ , and  $V_{\text{min}}^* = V_{\text{Scp}(\text{Scn})}^*$  in (4) or (5).  $V_{\text{Sap}} = V_{\text{max},\text{Sp}}$ ,  $V_{\text{San}} = V_{\text{max},\text{Sn}}$ ,  $V_{\text{Sbp}} = V_{\text{mid},\text{Sp}}$ ,  $V_{\text{Sbn}} =$  $V_{\text{mid},\text{Sn}}$ ,  $V_{\text{Scp}} = V_{\text{min},\text{Sp}}$ , and  $V_{\text{Scn}} = V_{\text{min},\text{Sn}}$  are the modified modulation waveform expressions for MCPWM + 1P ST in Fig. 5

$$\begin{cases} V_{\max\_Sp}(\omega t) = V_{\max}^{*}(\omega t) + \frac{1}{2}d_{ST}(\omega t) \\ V_{\max\_Sn}(\omega t) = V_{\max}^{*}(\omega t) + \frac{1}{6}d_{ST}(\omega t) \\ V_{\min\_Sp}(\omega t) = V_{\min}^{*}(\omega t) + \frac{1}{6}d_{ST}(\omega t) \\ V_{\min\_Sn}(\omega t) = V_{\min}^{*}(\omega t) - \frac{1}{6}d_{ST}(\omega t) \\ V_{\min\_Sp}(\omega t) = V_{\min}^{*}(\omega t) - \frac{1}{6}d_{ST}(\omega t) \\ V_{\min\_Sn}(\omega t) = V_{\min}^{*}(\omega t) - \frac{1}{2}d_{ST}(\omega t) \end{cases}$$

(11)

Fig. 6. MCPWM with 3P ST (MCPWM + 3P ST). (a) Equivalent carrier wave based PWM. (b) Switching states in the first sextant  $(0 \le \omega t \le \pi/3)$ .

where the subscript max, mid, and min refer to the phase of maximum, middle, and minimum output voltage.

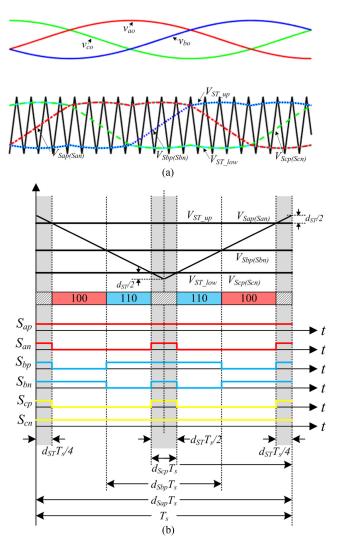

# B. SCPWM + 3P ST and MCPWM + 3P ST

Fig. 6 shows the equivalent carrier wave based PWM and the switching state for MCPWM + 3P ST. 3P ST method inserts ST interval in three-phase legs to replace zero state. The instantaneous ST current is averagely distributed among three-phase legs, which is beneficial to reduce the current stress and conduction loss of power devices. However, it introduces an additional switching commutation. As shown in Fig. 6, two straight lines  $V_{\rm ST\_up}$  and  $V_{\rm ST\_low}$  compared with triangular waveform are adopted to control ST interval [17]. During non-ST interval, control references of six switches for Z-source inverter are the same as modulation waveforms of conventional VSI expressed in (5) in the first sextant

$$\begin{cases} V_{\rm ST\_up}(\omega t) = 1 - \frac{1}{2} d_{\rm ST}(\omega t) \\ V_{\rm max\_Sp(Sn)}(\omega t) = V_{\rm max}^*(\omega t) \\ V_{\rm mid\_Sp(Sn)}(\omega t) = V_{\rm mid}^*(\omega t) \\ V_{\rm min\_Sp(Sn)}(\omega t) = V_{\rm min}^*(\omega t) \\ V_{\rm ST\_low}(\omega t) = \frac{1}{2} d_{\rm ST}(\omega t) \end{cases}$$

(12)

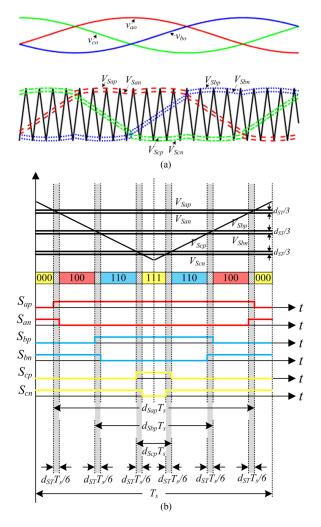

Fig. 7. MPWM with 1P ST (MPWM + 1P ST). (a) Equivalent carrier wave based PWM. (b) Switching states in the first sextant ( $0 \le \omega t \le \pi/3$ ).

# C. MPWM + 1PST

When MPWM is applied, all the zero-state intervals shown in Fig. 4 are used for ST. Thus, from (5), the ST duty ratio in the first sextant can be calculated as (10). And it changes with six-time line frequency. Fig. 7 shows the equivalent carrier wave based PWM and the switching state for MPWM + 1P ST [16], [19]. Substituting (10) into (11), the modulation waveforms of six switches can be rewritten as

$$\begin{cases}

V_{\text{max},\text{Sp}}(\omega t) = 1 \\

V_{\text{max},\text{Sn}}(\omega t) = V_{\text{max}}^{*}(\omega t) + \frac{1}{6}d_{\text{ST}}(\omega t) \\

V_{\text{mid},\text{Sp}}(\omega t) = V_{\text{mid}}^{*}(\omega t) + \frac{1}{6}d_{\text{ST}}(\omega t) \\

V_{\text{mid},\text{Sn}}(\omega t) = V_{\text{mid}}^{*}(\omega t) - \frac{1}{6}d_{\text{ST}}(\omega t) \\

V_{\text{min},\text{Sp}}(\omega t) = V_{\text{min}}^{*}(\omega t) - \frac{1}{6}d_{\text{ST}}(\omega t) \\

V_{\text{min},\text{Sn}}(\omega t) = 0

\end{cases}$$

(13)

Fig. 8. MPWM with 3P ST (MPWM + 3P ST). (a) Equivalent carrier wave based PWM. (b) Switching states in the first sextant  $(0 \le \omega t \le \pi/3)$ .

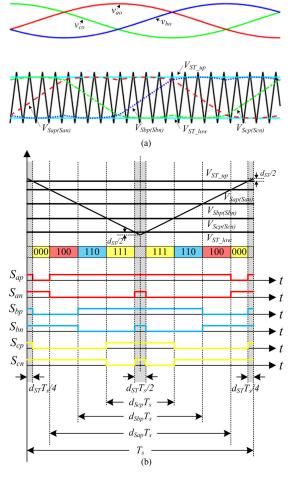

# D. MPWM + 3PST

Fig. 8 shows the equivalent carrier wave based PWM and the switching state for MPWM + 3P ST. Two curves  $V_{\text{ST\_up}}$  and  $V_{\text{ST\_low}}$  for ST interval control are the instantaneous maximum and minimum value of three-phase modulation waveforms. The control references of six switches can be written as

$$\begin{cases} V_{\mathrm{ST}}_{\mathrm{up}}(\omega t) = V_{\mathrm{max}}_{\mathrm{Sp}(\mathrm{Sn})}(\omega t) \\ V_{\mathrm{max}}_{\mathrm{Sp}(\mathrm{Sn})}(\omega t) = V_{\mathrm{max}}^{*}(\omega t) \\ V_{\mathrm{mid}}_{\mathrm{Sp}(\mathrm{Sn})}(\omega t) = V_{\mathrm{mid}}^{*}(\omega t) \\ V_{\mathrm{min}}_{\mathrm{Sp}(\mathrm{Sn})}(\omega t) = V_{\mathrm{min}}^{*}(\omega t) \\ V_{\mathrm{ST}}_{\mathrm{low}}(\omega t) = V_{\mathrm{min}}_{\mathrm{Sp}(\mathrm{Sn})}(\omega t) \end{cases}$$

(14)

## III. IPWM STRATEGY OF Z-SOURCE INVERTER

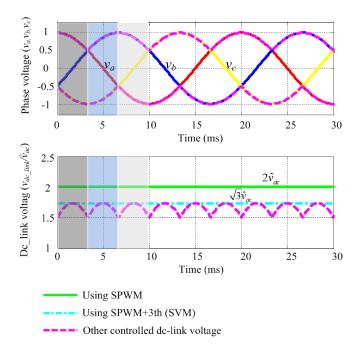

Fig. 9 shows the relationship of three-phase output voltage and available minimum dc-link voltage for conventional threephase VSI with SPWM and SVM. The fundamental frequency  $f_{\text{line}}$  is 50 Hz for analysis. Using SPWM, the minimum constant dc-link voltage is twice the peak value of output phase voltage

Fig. 9. Available dc-link voltage of the inverter bridge.

$2\hat{v}_{ac}$ , which is represented by the green solid line. Using SPWM with 3rd harmonic injection or SVM to increase dc-link voltage utilization, the minimum constant dc-link voltage is  $\sqrt{3}\hat{v}_{ac}$ , which is represented by the blue dot-dash line. Besides, there is another available dc-link voltage, which is represented by the magenta dashed line changing with six-time line frequency. It is actually the instantaneous maximum value of three-phase line voltage and it can be expressed as

$$v_{\rm dc\_link}^*(\omega t) = \sqrt{3} \cdot \hat{v}_{\rm ac} \cdot \cos\left(\theta - \frac{\pi}{6}\right)$$

(15)

where  $\theta$  is the remainder of  $\omega t$  divided by  $\pi/3$ ,  $\theta = \omega t \% (\pi/3)$ .

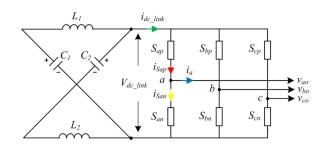

If the average dc-link voltage in one switching time period  $\langle v_{\rm dc,link} \rangle_{Ts}$  can be accurately controlled as the magenta dashed line shown in Fig. 9, the upper switch in the leg of the maximum phase voltage  $(v_{\rm max})$  and the lower switch in the leg of minimum phase voltage  $(v_{\rm min})$  are always turned ON. The upper and lower switches in the rest phase leg  $(v_{\rm mid})$  are controlled with PWM signal. The switching states of power devices in three-phase legs are listed in Table I. The equivalent switching frequency of power devices can be reduced to  $1/3f_s$  ( $f_s = 1/T_s$ ). Take the first sextant, for example, the instantaneous dc-link voltage is the line voltage  $(v_{\rm ao} - v_{\rm co})$ .  $S_{\rm ap}$  and  $S_{\rm cn}$  are always turned ON.  $S_{\rm bp}$  and  $S_{\rm bn}$  are controlled with PWM to regulate  $v_{\rm bo}$ . In each sextant, only one phase leg operates under complementary PWM mode. And the corresponding duty ratio of upper and lower switch  $d_{\rm Sip}^*$ ,  $d_{\rm Sin}^*$  are expressed as

$$\begin{cases} d_{\rm Sip}^*(\omega t) = \frac{v_{\rm mid}(\omega t) - v_{\rm min}(\omega t)}{v_{\rm max}(\omega t) - v_{\rm min}(\omega t)} \\ d_{\rm Sin}^*(\omega t) = 1 - d_{\rm Sip}^*(\omega t) \end{cases}$$

(16)

where in each sextant,  $v_{\min}(\omega t) = \min(v_{ao}, v_{bo}, v_{co}); v_{\max}(\omega t) = max(v_{ao}, v_{bo}, v_{co}); v_{\min}(\omega t) = \min(v_{ao}, v_{bo}, v_{co});$

TABLE I

Switching States of Power Devices in the Inverter Bridge

| Phase angle | $0^\circ \le \theta \ \le 60^\circ$ | $60^\circ \le \theta \le 120^\circ$ | $120^\circ \le \theta \le 180^\circ$ | $180^\circ \le \theta \le 240^\circ$ | $240^\circ \le \theta \le 300^\circ$ | $300^\circ \le \theta \le 360^\circ$   |

|-------------|-------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------|

| Mod A       | $S_{\rm ap} = 1;  S_{\rm an} = 0$   | $S_{\rm ap}\;S_{\rm an}={\rm PWM}$  | $S_{\rm ap} = 0;  S_{\rm an} = 1$    | $S_{\rm ap} = 0;  S_{\rm an} = 1$    | $S_{\rm ap}\;S_{\rm an}={\rm PWM}$   | $S_{\rm ap} = 1;  S_{\rm an} = 0$      |

| Mod B       | $S_{bp} S_{bn} = PWM$               | $S_{\rm bp} = 1; S_{\rm bn} = 0$    | $S_{\rm bp} = 1; S_{\rm bn} = 0$     | $S_{bp} S_{bn} = PWM$                | $S_{\rm bp} = 0; S_{\rm bn} = 1$     | $S_{\rm bp} = 0;  S_{\rm bn} = 1$      |

| Mod C       | $S_{\rm cp}=0;S_{\rm cn}=1$         | $S_{\rm cp}=0;S_{\rm cn}=1$         | $S_{\rm cp}\;S_{\rm cn}={\rm PWM}$   | $S_{\rm cp} = 1;  S_{\rm cn} = 0$    | $S_{\rm cp} = 1; S_{\rm cn} = 0$     | $S_{\rm cp} \; S_{\rm cn} = {\rm PWM}$ |

Fig. 10. Equivalent circuit of Z-source inverter viewed from the dc-link of the inverter bridge. (a) During ST interval. (b) During non-ST interval.

and *i* representing the phase of  $v_{\rm mid}(\omega t)$  changes between *a*, *b*, and *c*.

As for conventional two-stage buck–boost VSI, at the intermediate dc link, there is a large aluminum electrolytic capacitor to absorb the high frequency current harmonics and compensate the transient power difference between the front boost circuit and inverter bridge [32]. Usually, the intermediate dc-link voltage is kept almost constant by adjusting the boost duty ratio in steady state. It is difficult or even impossible to control the intermediate dc-link voltage like a six-pulse waveform. However, for Z-source inverter,  $v_{dc_link}$  is chopped dc voltage with high switching frequency. Therefore, maybe there is a new PWM strategy that is suitable for Z-source inverter.

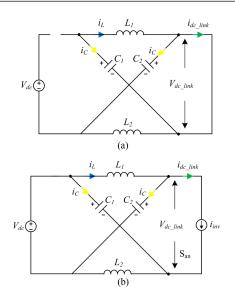

According to the operation principles of Z-source inverter described in Peng [3], Fig. 10 shows two equivalent circuits seen from the dc link of the inverter bridge. During ST interval,  $D_0$  is reverse biased and Z-source network is shorted  $v_{dc,link} = 0$ . During non-ST interval,  $D_0$  is conducting, both capacitors and dc source are reversely connected to supply the inverter bridge  $v_{dc,link} = 2V_C - V_{dc}$ . Thus, the average intermediate dc-link voltage in one switching time period is calculated in the following equation:

$$< v_{\rm dc \ link} >_{T_s} = \frac{1}{T_s} \cdot \left( \int_0^{d_{\rm ST} \cdot T_s} 0 dt + \int_{d_{\rm ST} \cdot T_s}^{T_s} (2V_C - V_{\rm dc}) dt \right)$$

$$= (1 - d_{\rm ST}) \cdot (2V_C - V_{\rm dc}). \tag{17}$$

From (17),  $\langle v_{dc,link} \rangle_{Ts}$  can be regulated intermediately by adjusting  $d_{ST}$ . For simple analysis, it is assumed that the capacitance of  $C_1$  and  $C_2$  is large enough and the voltage is almost constant in steady state. In order to reduce the switching frequency of power devices in the inverter bridge so that a higher efficiency can be attained, it is possible to regulate  $\langle v_{dc,link} \rangle_{Ts}$  to meet (15). Obviously,  $d_{ST}$  is periodically changing in every 60° (1/6 output line frequency period)

$$(1 - d_{\rm ST}(\omega t)) \cdot (2V_C - V_{\rm dc}) = \sqrt{3} \cdot \hat{v}_{\rm ac} \cdot \cos\left(\theta - \frac{\pi}{6}\right)$$

(18)

where  $\theta$  is the remainder of  $\omega t$  divided by  $\pi/3$ ,  $\theta = \omega t \% (\pi/3)$ .

In this case, the average voltage of inductor in one sextant should be zero, according to volt-second balance principle

$$\frac{3}{\pi} \int_0^{\pi/3} \left( d_{\rm ST}(\omega t) T_s \cdot V_C + (1 - d_{\rm ST}(\omega t)) T_s \right)$$

$$\cdot \left( V_{\rm dc} - V_C \right) d\omega t = 0.$$

(19)

Ignoring the low frequency ripples associated with output line frequency  $f_{\text{line}}$ ,  $V_C$  is determined by the average value of ST duty ratio  $d_{\text{avg}}$

$$V_C = \frac{1 - \frac{3}{\pi} \int_0^{\pi/3} d_{\rm ST}(\omega t) d\omega t}{1 - 2 \cdot \frac{3}{\pi} \int_0^{\pi/3} d_{\rm ST}(\omega t) d\omega t} V_{\rm dc} = \frac{(1 - d_{\rm avg}) V_{\rm dc}}{1 - 2 d_{\rm avg}}$$

(20)

in which,  $d_{\rm avg}$  can be calculated by integrating  $d_{\rm ST}(\omega t)$  in (18) in one sextant

$$d_{\text{avg}} = \frac{3}{\pi} \cdot \int_0^{\pi/3} \left( 1 - \frac{v_{\text{dc\_link}}(\omega t)}{2V_C - V_{\text{dc}}} \right) \cdot d\omega t$$

$$= 1 - \frac{3\sqrt{3}}{\pi} \cdot \frac{\hat{v}_{\text{ac}}}{2V_C - V_{\text{dc}}}.$$

(21)

Solving (6), (20), and (21), the capacitor voltage in steady state can be derived as

$$V_C = \frac{3\sqrt{3}G}{2\pi} \cdot V_{\rm dc}.$$

(22)

And the ST duty ratio is

$$d_{\rm ST}(\omega t) = 1 - \frac{\pi}{3} (1 - d_{\rm avg}) \cos\left(\omega t - \frac{\pi}{6}\right)$$

(23)

$$d_{\rm avg} = \frac{3\sqrt{3}G - 2\pi}{6\sqrt{3}G - 2\pi}.$$

(24)

When Z-source inverter operates under boost mode,  $d_{ST}(\omega t) \ge 0$ . So G should be larger than 1.27 from (23) and (24).

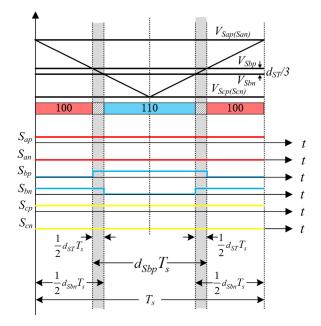

Fig. 11 shows the switching state of IPWM strategy for Z-source inverter in the first sextant. The ST interval is symmetrically inserted into the phase-leg of  $v_{\rm mid}$ . In the first sextant, the output three-phase voltage meet  $v_{\rm max} = v_{\rm ao}$ ,  $v_{\rm mid} = v_{\rm bo}$ , and  $v_{\rm min} = v_{\rm co}$ . The thick-shaded part represents the ST

Fig. 11. Switching states of Z-source inverter with IPWM strategy in the first sextant.

interval, which serves to regulate the intermediate dc-link voltage ( $\langle v_{dc,link} \rangle_{T_s} = v_{ao} - v_{co}$ ). The active voltage vectors (110, 100) are implemented during non-ST interval to regulate  $v_{bo}$ . For symmetry, the switching states in other sextants can be obtained similarly. Since only power devices in one phase leg operate at high switching frequency, IPWM + 1P ST can minimize the equivalent switching frequency of power devices in the inverter bridge. As a result, it can be predicted that the switching loss will be reduced to a great extent. As shown in Fig. 11, according to volt-second balance principle, the duty ratio of upper switch  $d_{Sip}$  and lower switch  $d_{Sin}$ , output voltage of phase  $B v_{mid}$  meets

$$\begin{cases} v_{\rm mid}(\omega t) - v_{\rm min}(\omega t) = (d_{\rm Sbp}(\omega t) - d_{\rm ST}(\omega t)) \cdot (2V_C - V_{\rm dc}) \\ d_{\rm Sbn}(\omega t) = 1 - d_{\rm Sbp}(\omega t) + d_{\rm ST}(\omega t). \end{cases}$$

(25)

Furthermore,  $\langle v_{dc_{link}} \rangle_{Ts}$  is controlled the same as maximum value of three-phase line voltage

$$(1 - d_{\rm ST}(\omega t)) \cdot (2V_C - V_{\rm dc}) = v_{\rm max}(\omega t) - v_{\rm min}(\omega t).$$

(26)

Combining (24)–(26), the corresponding duty ratio expressions of the upper and lower switches  $d_{\text{Sip}}$  and  $d_{\text{Sin}}$  in (16) can be modified as

$$\begin{cases} d_{\rm Sip}(\omega t) = \frac{v_i(\omega t) - v_{\rm min}(\omega t)}{v_{\rm max}(\omega t) - v_{\rm min}(\omega t)} \cdot (1 - d_{\rm ST}(\omega t)) + d_{\rm ST}(\omega t) \\ d_{\rm Sin}(\omega t) = 1 - d_{\rm Sip}(\omega t) + d_{\rm ST}(\omega t). \end{cases}$$

(27)

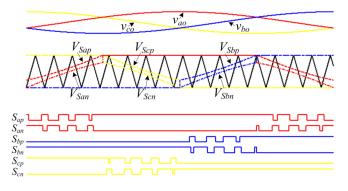

Like the typical PWM strategies of Z-source inverter, IPWM + 1P ST can be obtained by the level shift of conventional threephase VSI modulation waveforms. Fig. 12 shows the equivalent carrier wave based PWM and switching state for IPWM + 1P ST. Six modulation waveforms are compared with the triangular wave to produce the gate signals for switches in

Fig. 12. Equivalent carrier waveform based PWM for IPWM + 1P ST.

Z-source inverter. Assume the amplitude of triangular wave is normalized, the modulation waveform expressions of six switches are expressed as follows:

$$\begin{cases} V_{\text{max}\_\text{Sp}}(\omega t) = V_{\text{max}\_\text{Sn}}(\omega t) = 1\\ V_{\text{mid}\_\text{Sp}}(\omega t) = V_{\text{mid}}^*(\omega t) + \frac{1}{2}d_{\text{ST}}(\omega t)\\ V_{\text{mid}\_\text{Sn}}(\omega t) = V_{\text{mid}}^*(\omega t) - \frac{1}{2}d_{\text{ST}}(\omega t)\\ V_{\text{min}\_\text{Sp}}(\omega t) = V_{\text{min}\_\text{Sn}}(\omega t) = 0 \end{cases}$$

(28)

where  $V_{\text{mid}}^*$  refer to the modulation of conventional three-phase VSI in (5).

# IV. COMPARISON OF PWM STRATEGIES

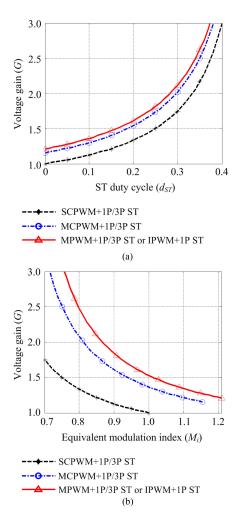

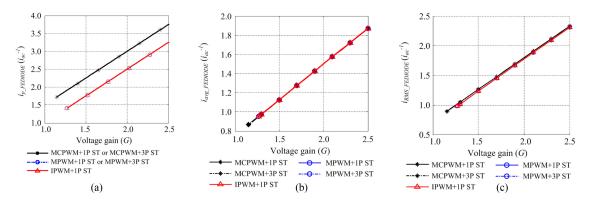

To investigate the inherent advantages and disadvantages of IPWM + 1P ST, comparisons with the typical PWM strategies are carried out in terms of voltage boost capability, the requirements of power devices and passive components. According to the operation principle of Z-source inverter using different PWM strategies, the steady-state operation points including voltage gain G, ST interval  $d_{ST}$ , capacitor voltage  $V_C$ , and inductor current  $I_L$  can be derived and listed in Table II. The voltage gain comparison of Z-source inverter with different PWM strategies is shown in Fig. 13. Due to full utilization of intermediate dc-link voltage, IPWM + 1P ST and MPWM + 1P/3P ST have the maximum voltage boost capability.

## A. Power Devices Comparison

As for Z-source inverter using SCPWM + 1P ST and MCPWM + 1P ST shown in Fig. 5, the switching frequency of power devices in the inverter bridge and  $D_0$  are  $f_s$  and  $6f_s$  ( $f_s = 1/T_s$ ), respectively. For Z-source inverter using MPWM + 1P ST shown in Fig. 7, the switching frequency of power devices in the inverter bridge and  $D_0$  are  $2/3f_s$  and  $4f_s$ , respectively. IPWM + 1P ST uses single-phase leg for ST current conduction without introducing an additional switching communication, which is different from the existing PWM strategies. The equivalent switching frequency is reduced to  $1/3f_s$ , which is the minimum value among the existing PWM strategies. Table III lists the equivalent switching frequency of power devices for Z-source inverter with different PWM strategies ( $f_s = 1/T_s$ ).

Modulation scheme SCPWM + 1P ST [3], SCPWM + 3P ST [3], MCPWM + 1P ST [17], MCPWM + 3P ST MPWM + 1P ST [16] MPWM + 3P ST [16] IPWM + 1P ST [17].  $G\,=\,\frac{1\,-d_{\,{\rm S}\,{\rm T}}}{1\,-2\,d_{\,{\rm S}\,{\rm T}}}\,=\,\frac{M_{\,i}}{2\,M_{\,i}\,-1}$ da<u>vg</u>  $\frac{-d_{ST}}{-2d_{ST}}$ Voltage gain(G)G =G = $\sqrt{3}M$  $3\sqrt{3}M$  $d_{ST} = 1 - M_i = \frac{G-1}{2G-1}$ ST interval $(d_{ST} \text{ or } d_{avg})$  $d_{ST} = 1 - \frac{\sqrt{3}}{2}M_i$ = 1 $\frac{3\sqrt{3}}{2\pi}M_i$ =  $M_i = 1 - d_{\mathrm{ST}} = \frac{G}{2G - 1}$  $\frac{2\pi}{2\pi}(1 - d_{avg})$ Modulation index  $(M_i)$  $M_i$  $\frac{2}{\sqrt{3}}(1 - d_{ST}) =$  $\frac{\sqrt{3}}{1-d_{\mathrm{ST}}}V_{\mathrm{dc}} = \frac{\sqrt{3}}{2} V_{\mathrm{dc}}$  $V_C = \frac{1 - d_{ST}}{1 - 2 d_{ST}} V_{dc} = G V_{dc}$  $\frac{V_{davg}}{-2 davg} V_{dc}$ Capacitor voltage( $V_{\rm C}$ )  $V_C$ 3 \ davg î.  $i_L = \frac{3}{4}G\hat{i}_{ac} = \frac{3}{4}\frac{1-d_{ST}}{1-2d_{ST}}\hat{i}_{ac}$ dst î. Inductor  $current(I_{L})$  $i_L = \frac{3}{4}G\hat{i}_{ac} = \frac{3}{2\sqrt{3}}$  $i_L = \frac{3}{4}G\hat{i}_{ac} = \frac{\pi}{2\sqrt{3}}$  $1 - 2d_{ax}$

TABLE II

EXPRESSIONS OF VOLTAGE GAIN FOR Z-SOURCE INVERTER WITH DIFFERENT PWM STRATEGIES

Fig. 13. Voltage gain of Z-source inverter with different modulation strategies. (a) G and  $d_{ST}$ . (b) G and  $M_i$ .

| TABLE III                                                    |  |  |  |  |

|--------------------------------------------------------------|--|--|--|--|

| EQUIVALENT SWITCHING FREQUENCY OF POWER DEVICES FOR Z-SOURCE |  |  |  |  |

| Inverter With Different PWM Strategies $(f_s = 1/T_s)$       |  |  |  |  |

|                                   | Switching frequency |                             |  |

|-----------------------------------|---------------------|-----------------------------|--|

| Modulation scheme                 | Front diode         | Switches in inverter bridge |  |

| SCPWM + 3P ST, MCPWM + 3P ST [17] | $2f_s$              | $2f_s$                      |  |

| SCPWM + 1P ST, MCPWM + 1P ST [17] | $6 f_s$             | $f_s$                       |  |

| MPWM + 3P ST [16]                 | $2f_s$              | $4f_{s}/3$                  |  |

| MPWM+ 1P ST [16]                  | $4f_s$              | $2f_s/3$                    |  |

| IPWM + 1P ST                      | $2f_s$              | $f_s/3$                     |  |

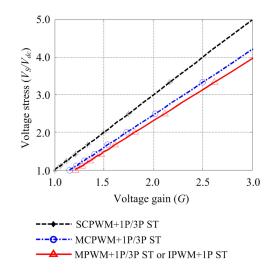

Fig. 14. Voltage stress of power device for Z-source inverter with different PWM strategies.

According to the operation principle of Z-source inverter,  $D_0$  and switching devices in the inverter bridge withstand the same voltage stress, which is the maximum of intermediate dc-link voltage in the following equation:

$$v_s = 2V_C - V_{\rm dc}.\tag{29}$$

For existing PWM strategies and IPWM, substituting  $V_C$  listed in Table II into (29), the voltage stress of power devices as function of voltage gain *G* can be derived as follows:

$$v_s = (2G - 1)V_{dc}$$

(SCPWM + 1P/3P ST) (30)

$$v_s = \frac{\sqrt{3G-2}}{2} V_{\rm dc}$$

(MCPWM + 1P/3P ST) (31)

$$v_s = \frac{3\sqrt{3}G - 2\pi}{2\pi} V_{dc}$$

(MPWM + 1P/3P ST or IPWM + 1P ST). (32)

Fig. 14 shows the power devices voltage stress comparison for Z-source inverter with different PWM strategies. MPWM strategies (IPWM + 1P ST and MPWM + 1P/3P ST) have the minimum voltage stress of power devices.

In addition to voltage stress, another key parameter for the selection of power device is the current stress  $(I_S)$ . The three typical indicators reflecting power device current stress are as follows:

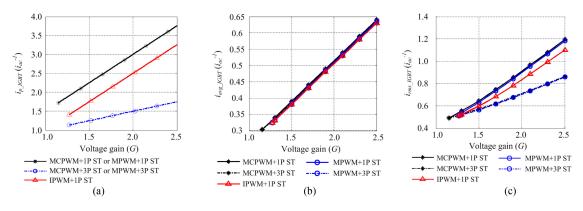

Fig. 15. Current stress of insulated-gate bipolar transistor (IGBT)  $(\cos(\varphi) = 1)$ . (a)  $i_{p \perp IGBT}$ . (b)  $i_{avg \perp IGBT}$ . (c)  $i_{rm s \perp IGBT}$ .

Fig. 16. Current stress of free-wheeling diode ( $\cos(\varphi) = 1$ ). (a)  $i_{p \text{-FWDIODE}}$ . (b)  $i_{\text{avg}\text{-FWDIODE}}$ . (c)  $i_{\text{rms}\text{-FWDIODE}}$ .

- 1)  $I_{S_{\text{peak}}}$ , the maximum instant current flowing through the power device defined as (33);

- 2)  $I_{S_{avg}}$ , the average current flowing through power device in each output line-frequency period defined as (34);

- 3)  $I_{S_{\rm rms}}$ , the root mean square (rms) value of current flowing through power device in each output line-frequency period defined as (35) [32]

$$I_{S_{\text{-peak}}} = \max(i_S(\omega t)) \tag{33}$$

$$I_{S_{\text{avg}}} = \frac{1}{2\pi} \begin{bmatrix} \int_0^{2\pi} d_{\text{ST}}(\omega t) \cdot i_{S_{\text{ST}}}(\omega t) d(\omega t) \\ + \int_0^{2\pi} d_{\text{NST}}(\omega t) \cdot i_{S_{\text{NST}}}(\omega t) d(\omega t) \end{bmatrix} (34)$$

$$I_{S,\rm rms} = \sqrt{\frac{1}{2\pi} \begin{bmatrix} \int_0^{2\pi} d_{\rm ST}(\omega t) \cdot i_{\rm ST}^2(\omega t) d(\omega t) \\ + \int_0^{2\pi} d_{\rm NST}(\omega t) \cdot i_{\rm NST}^2(\omega t) d(\omega t) \end{bmatrix}} (35)$$

According to the definition in (33)–(35), the average and rms current calculation depends on the on-state duty ratio and current across power device. The mathematic expressions of on-state duty ratio and on-state current in different switching states are derived in the Appendix. Then, it is easier to use numerical calculation to get the comparison results.

Figs. 15–17 show the current stress of insulated-gate bipolar transistor (IGBT), free-wheeling diode, and  $D_0$  for Zsource inverter with different PWM strategies, respectively. The load power factor is unit 1 here ( $\cos(\varphi) = 1$ ). As shown in Fig. 15(a), MCPWM + 3P ST and MPWM + 3P ST have the minimum peak current. It is because the large ST current is simultaneously distributed among three-phase legs. Compared with MCPWM + 1P ST and MPWM + 1P ST, IPWM + 1P ST is beneficial to reduce IGBT peak current. This is because the ST interval is inserted in the phase of  $v_{\rm mid}$ . As shown in Fig. 15(b), all these PWM strategies have almost the same average current stress of IGBT. This is because eventually the ST current is averagely distributed among three-phase legs in each output line-frequency period. ( $T_{\rm line} = 1/f_{\rm line}$ ). When it comes to rms current of IGBT, PWM with 3P ST (MCPWM + 3P ST, MPWM + 3P ST) have the minimum value compared to those with 1P ST (MCPWM + 1P ST, MPWM + 1P ST, IPWM + 1P ST). IPWM + 1P ST has a little smaller value of rms current than that of MCPWM + 1P ST, MPWM + 1P ST.

As shown in Fig. 16(a), with MPWM strategies (MPWM + 1P/3P ST, IPWM + 1P ST), free-wheeling diode has the minimum peak current, which is half of MCPWM (MCPWM+1P/3P ST). With MPWM+3P ST and IPWM+1P ST, free-wheeling diode has the minimum average current and RMS current shown in Fig. 16(b) and Fig. 16(c). Under the high load power factor, the average and RMS current of free-wheeling diode are far smaller than that of IGBT.

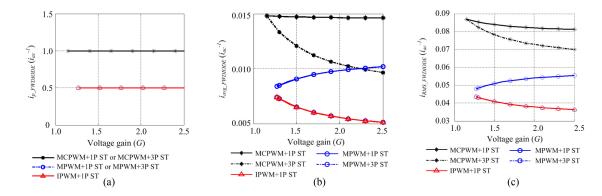

As shown in Fig. 17, MPWM strategies (MPWM + 1P/3P ST, IPWM + 1P ST) have the minimum value of peak current for  $D_0$ . With different PWM strategies, the average current flowing through  $D_0$  is the input current under certain output power. Thus, they have the same value of average current shown in Fig. 17(b). Compared with MCPWM strategies (MCPWM + 1P/3P ST),

Fig. 17. Current stress of front-end diode ( $\cos(\varphi) = 1$ ). (a)  $i_{p \, \text{FEDIODE}}$ . (b)  $i_{\text{avg},\text{FEDIODE}}$ . (c)  $i_{\text{rms},\text{FEDIODE}}$ .

MPWM strategies (MPWM + 1P/3P ST, IPWM + 1P ST) have a little smaller value of rms current.

In all, for Z-source inverter, PWM strategies with different ST injection methods mainly affect the current stress of IGBT, but have little influence on the average and rms current of free-wheeling diode and the front-end diode. Z-source inverter with IPWM + 1P ST demonstrates the maximum voltage boost capability, minimum voltage stress, and minimum switching frequency of power devices.

## B. Passive Components Requirement Comparison

In general, the cost and volume of passive component are proportional to the available energy stored in it. The inductor core and winding are designed on the basis of the inductance requirement (L) and average current level ( $I_L$ ) under maximum operation conditions. The inductance is selected to limit the current ripples in a certain range. The capacitor is designed based on the current capacity, capacitance requirement, and terminal voltage [27]. The current capacity usually refers to the rms value of the current ripples, which is related the capacitor working temperature and service life. The capacitance is selected according to the limitations of the voltage ripple. The current/voltage ripples of inductor/capacitor are defined as

$$\Delta I_L = \delta_L \cdot I_L \tag{36}$$

$$\Delta V_C = \delta_C \cdot V_C \tag{37}$$

where  $\delta_L$  and  $\delta_C$  are the ripples coefficients preset based on the performance indices of power converter.

As for MCPWM (MCPWM + 1P/3P ST),  $d_{ST}$  in one switching time period is constant. Thus, in theory, passive components just contain switching-frequency ripples, which are analyzed in one switching time period  $T_s$ .  $I_L$  increases during ST interval and decreases during non-ST interval, whereas  $v_C$  decreases during ST interval and increases during non-ST interval.

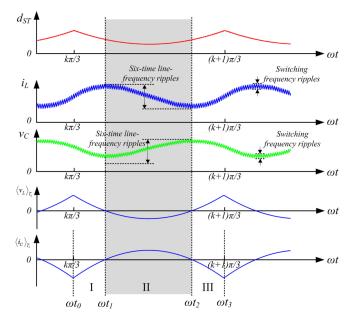

With MPWM strategies (MPWM + 1P/3P ST, IPWM + 1P ST),  $d_{ST}$  expressed in (23) keeps changing in each sextant. The typical waveforms of inductor current and capacitor voltage are shown in Fig. 18, in which,  $\langle v_L \rangle_{Ts}$  is the average value of inductor terminal voltage in one switching time period, and  $\langle i_C \rangle_{Ts}$  is the average value of capacitor current in one switching time period. In theory, besides the switching frequency ripples, the passive components also

615

Fig. 18. Inductor current and capacitor voltage waveforms for Z-source inverter with MPWM strategies (MPWM + 1P/3P ST or IPWM + 1P ST).

contain six-time-line-frequency ripples, which are analyzed in one sextant. Usually, the amplitude of switching frequency ripples is much smaller than that of six-time-line-frequency ripples. Thus, the inductance and capacitance in Z-source network should be designed to limit the low-frequency ripples in the desired range. As shown in Fig. 18,  $i_L$  increases and  $v_C$ decreases during interval II ( $\omega t_1, \omega t_2$ ). According to inductor's V–I characteristic,  $\Delta I_L$  can be calculated by integrating  $\langle v_L \rangle_{Ts}$  from  $\omega t_1$  to  $\omega t_2$ . Similarly,  $\Delta v_C$  can be derived by integrating  $\langle i_C \rangle_{Ts}$  from  $\omega t_1$  to  $\omega t_2$ . The detailed derivation process is in the Appendix. Table IV lists the expressions of inductance and capacitance requirement for Z-source inverter with different PWM strategies.

For Z-source inverter with the different PWM strategies, the current of capacitor keeps changing periodically in every sextant. Thus, the rms current of capacitor can be calculated by integrating  $i_C$  in 60°. The expressions of duty ratio and capacitor current in different switching states are derived in the

TABLE IV EXPRESSIONS OF PASSIVE COMPONENTS REQUIREMENT FOR Z-SOURCE INVERTER WITH DIFFERENT PWM STRATEGIES

| Modulation scheme                 | Inductance (L)                                                                                                                                   | Capacitance (C)                                                                                                                |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| MCPWM + 3P ST<br>[17]             | $L = \frac{1}{2\sqrt{3}} \cdot \frac{\sqrt{3}G - 2}{\sqrt{3}G - 1} \cdot \frac{V_{\mathrm{dc}}}{\delta_L \cdot f_s \cdot \hat{i}_{\mathrm{ac}}}$ | $C = \frac{\sqrt{3}}{8} \cdot \frac{\sqrt{3}G - 2}{\sqrt{3}G - 1} \cdot \frac{\hat{i}_{ac}}{\delta_C \cdot f_s \cdot V_{dc}}$  |

| MCPWM + 1P ST<br>[17]             | $L = \frac{1}{6\sqrt{3}} \cdot \frac{\sqrt{3}G - 2}{\sqrt{3}G - 1} \cdot \frac{V_{\mathrm{dc}}}{\delta_L \cdot f_s \cdot \hat{i}_{\mathrm{ac}}}$ | $C = \frac{1}{8\sqrt{3}} \cdot \frac{\sqrt{3}G - 2}{\sqrt{3}G - 1} \cdot \frac{\hat{i}_{ac}}{\delta_C \cdot f_s \cdot V_{dc}}$ |

| MPWM+1P/3P ST<br>[16], IPWM+1P ST | $L = \frac{0.0181}{\sqrt{3}\pi} \cdot \frac{V_{\rm dc}}{\delta_L \cdot f_{\rm Line} \cdot \hat{i}_{\rm ac}}$                                     | $C = \frac{0.0181G}{4(3\sqrt{3}G - \pi)} \frac{\hat{i}_{ac}}{\delta_C \cdot f_{line} \cdot V_{dc}}$                            |

Fig. 19. Inductance requirement of Z-source inverter with different PWM strategies.

Appendix

$$I_{C_{\rm JTMS}}^2 = \frac{6}{T_{\rm Line}} \sum \Delta(t) \cdot i_C^2(t)$$

$$= \frac{3}{\pi} \left[ \int_0^{\pi/3} \left( d_{\rm ST}(\omega t) \cdot (i_C(\omega t))^2 + d_{\rm NST}(\omega t) \cdot (i_C(\omega t))^2 \right) d(\omega t) \right].$$

(38)

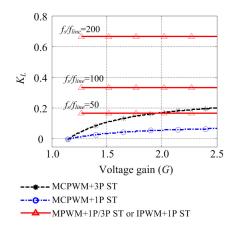

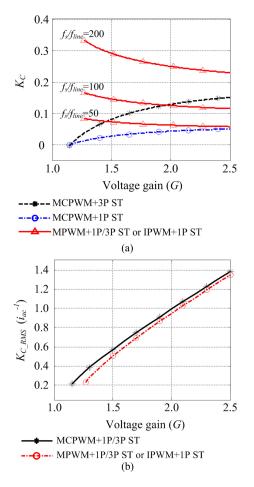

Based on the equations listed in Table IV and the aforementioned definitions, the relationship of passive components requirements versus voltage gain for Z-source inverter with different PWM strategies is shown in Figs. 19 and 20.  $f_s/f_{\text{line}}$ is the ratio of switching frequency over the output voltage line frequency. The parameters  $K_L$ ,  $K_C$ , and  $K_{C-\text{rms}}$  are defined as

$$K_L = \frac{L}{V_{\rm dc}/\delta_L f_s \hat{i}_{\rm ac}}$$

(39)

$$K_C = \frac{C}{\hat{i}_{\rm ac}/\delta_C f_s V_{\rm dc}} \tag{40}$$

$$K_{\rm IC} = \frac{I_{C\,\rm rms}}{\hat{i}_{\rm ac}} \tag{41}$$

where  $K_L$  reflects the inductance requirement, and  $K_C$  and  $K_{IC}$  reflect the capacitance requirement and current ripples of capacitor.

Based on the equations listed in Table II, under the same input and output operation condition, Z-source inverter with different PWM strategies has the same average current  $i_L$ . With MPWM

Fig. 20. Capacitor requirement of Z-source inverter with different PWM strategies. (a) Capacitance comparison. (b) RMS current of capacitor.

strategies (MPWM + 1P/3P ST and IPWM + 1P ST), it has the minimum capacitor voltage  $v_C$ . As shown in Figs. 19 and 20, MCPWM + 1P ST has the least inductance and capacitance requirement. With the increase of switching frequency, MCPWM + 1P/3P ST needs much smaller inductance and capacitance compared to MPWM + 1P/3P ST and IPWM + 1P ST. However, much high switching frequency causes large switching losses of power devices. The tradeoff between the size of passive components and power devices loss should be considered in practical application. Compared to MCPWM + 1P/3P ST, MPWM + 1P/3P ST and IPWM + 1P ST reduce the rms value of capacitor current ripples.

# V. CLOSED-LOOP CONTROLLER DESIGN

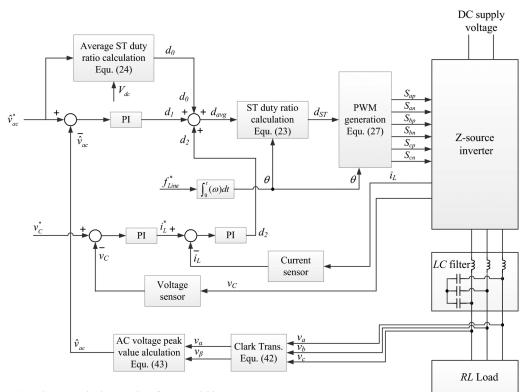

When Z-source inverter operates with constant boost control, there are two control variables:  $d_{\rm ST}$  and  $M_i$ . The intermediate capacitor voltage  $v_C$  is controlled by  $d_{\rm ST}$  and the output ac voltage is controlled by  $M_i$ , using separate controllers [27], [29]. However, when Z-source inverter operates with MPWM (IPWM + 1P ST), there is only one control freedom  $d_{\rm ST}$  for both regulation of  $v_C$  and  $\hat{v}_{\rm ac}$ . Fig. 21 shows the closed-loop control system diagram, which consists of the dc-side dualloop capacitor voltage control and the ac-side output voltage

Note: the superscript \* means the reference variables.

# Fig. 21. Control system diagram of Z-source inverter with IPWM + 1P ST.

control. For a given output voltage reference  $\hat{v}_{ac}^*$ , voltage gain G and reference capacitor voltage  $v_C^*$  are calculated by (6) and (22). With regarding to the nonlinear relationship of G and  $d_{avg}$  expressed in (24) and nonminimum phase characteristics of  $v_C$  and  $d_{avg}$  in (20), the feedforward control technique with  $\hat{v}_{ac}^*$  and input voltage  $V_{dc}$  is introduced to calculate the approximate value of average ST duty ratio  $d_0$  by (24). This is beneficial to achieve a good transient performance. For ac-side control, the amplitude of three-phase voltage is feedback because it is dc component.  $v_{ao}$ ,  $v_{bo}$ , and  $v_{co}$  are measured and transformed into  $v_{\alpha}$  and  $v_{\beta}$  in two-axis stationary reference frame according to the following equation:

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \frac{2}{3} \cdot \begin{bmatrix} 1 - \frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \cdot \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}$$

(42)

where factor 2/3 is included, which means that the amplitude of voltage vector equals to the peak value of the output phase voltage. Then,  $\hat{v}_{\rm ac}$  can be calculated by

$$\hat{v}_{\rm ac} = \sqrt{v_\alpha^2 + v_\beta^2}.\tag{43}$$

The proportional-integral (PI) controller output  $d_1$  makes sure three-phase output voltage follows the reference with zero steady-state error. The PI controller output  $d_2$  drives the dc-side capacitor voltage to follow  $V_C^*$ . The phase angle  $\theta$  determines which sextant the reference voltage vector is located in. The instantaneous ST duty ratio  $d_{\rm ST}$  is calculated based on  $d_{\rm avg}$  and  $\theta$  according to (23). Then, the PWM module generates PWM

Fig. 22. DC-side equivalent circuit.

signals for six power devices in Z-source inverter according to (27).

The state-space averaged model provides good understanding of circuit characteristic and tools for parameters design of PI controller. For Z-source inverter supplying three-phase balanced load, the ac-side can be transferred to dc-side and simplified as a resistive load connected with an essential *LC* filter. Fig. 22 shows the dc-side equivalent circuit. The equivalent load resistor is calculated based on power balance

$$R_e = \frac{18}{\pi^2} \cdot R_L. \tag{44}$$

By taking all the inductor current  $(i_L, i_{Lf})$  and capacitor voltage  $(v_C, v_{Cf})$  as the state variables and using the statespace averaging method in one switching time period  $(T_s)$ , the state equations of dc-side equivalent circuit can be expressed as the following equation:

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_C}{dt} \\ \frac{di_{Lf}}{dt} \\ \frac{di_{Lf}}{dt} \\ \frac{dv_{Cf}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & -\frac{1-2d_{\rm ST}}{L} & 0 & 0 \\ \frac{1-2d_{\rm ST}}{C} & 0 & -\frac{1-d_{\rm ST}}{C} & 0 \\ 0 & \frac{2(1-d_{\rm ST})}{L_f} & 0 & -\frac{1}{L_f} \\ 0 & 0 & \frac{1}{C_f} & -\frac{1}{C_fR_e} \end{bmatrix} \\ \times \begin{bmatrix} i_L \\ v_C \\ i_{Lf} \\ v_{Cf} \end{bmatrix} + \begin{bmatrix} \frac{1-d_{\rm ST}}{L} \\ 0 \\ -\frac{1-d_{\rm ST}}{L_f} \\ 0 \end{bmatrix} V_{\rm dc} \qquad (45)$$

$$G_{i_L}(s) = \frac{\hat{i}_L(s)}{\hat{d}_{\rm Son}(s)}$$

$$a_{13} \cdot s^3 + a_{12} \cdot s^2 + a_{11} \cdot s + a_{10} \qquad (45)$$

$$= \frac{a_{13} \cdot s^{*} + a_{12} \cdot s^{*} + a_{11} \cdot s + a_{10}}{b_4 \cdot s^4 + b_3 \cdot s^3 + b_2 \cdot s^2 + b_1 \cdot s + b_0}$$

(46)

$$G_{v_C}(s) = \frac{\hat{v}_C(s)}{\hat{d}_{c_0}(s)}$$

$$\hat{d}_{Son}(s) = \frac{a_{23} \cdot s^2 + a_{22} \cdot s^2 + a_{21} \cdot s + a_{20}}{b_4 \cdot s^4 + b_3 \cdot s^3 + b_2 \cdot s^2 + b_1 \cdot s + b_0}$$

(47)

$$\hat{v}_{Cf}(s)$$

$$G_{v_{Cf}}(s) = \frac{b_{Cf}(s)}{\hat{d}_{Son}(s)}$$

$$= \frac{a_{32} \cdot s^2 + a_{31} \cdot s + a_{30}}{b_4 \cdot s^4 + b_3 \cdot s^3 + b_2 \cdot s^2 + b_1 \cdot s + b_0}$$

(48)

where the numerator and denominator coefficients are as follows:

$$\begin{aligned} a_{13} &= CL_f C_f R_e \alpha, \, a_{12} = CL_f \alpha + (1-2D)C_f L_f R_e \beta \\ a_{11} &= (1-2D)L_f \beta + CR_e \alpha + (1-D)C_f R_e \alpha, \\ a_{10} &= 2(1-D)\alpha \\ a_{23} &= -LL_f C_f R_e \beta \\ a_{22} &= -LL_f \beta + [(1-D)L + (1-2D)L_f]C_f R_e \alpha, \\ a_{21} &= [(1-D)L + (1-2D)L_f]\alpha - LR_e \beta, \\ a_{20} &= (1-2D)R_e \alpha \\ a_{32} &= -LCR_e \alpha, a_{31} = -2(1-D)LR_e \beta, \\ a_{30} &= (1-2D)R_e \alpha \\ b_4 &= LCL_f C_f R_e, \, b_3 = LCL_f \\ b_2 &= LCR_e + (1-2D)^2 L_f C_f R_e + 2(1-D)^2 LC_f R_e \\ b_1 &= 2(1-D)^2 L + (1-2D)^2 L_f, \end{aligned}$$

Fig. 23. Block diagram of closed-loop controller for dc-side equivalent circuit.

$$b_0 = (1 - 2D)^2 R_e$$

$$\alpha = 2V_C - V_{dc} = \frac{1}{1 - d_{ST}} V_{dc},$$

$$\beta = 2I_L - I_{Lf} = \frac{1}{(1 - d_{ST})^2} \frac{V_{dc}}{R_e}.$$

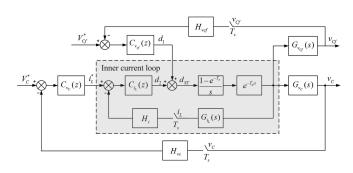

Performing small signal perturbation at the equilibrium operation point, the transfer functions of control to inductor current, intermediate capacitor voltage, and output voltage perturbations are derived as (46), (47), and (48), respectively.

It can be observed from (46) to (48) that the transfer functions of ST duty ratio to intermediate capacitor voltage  $G_{v_C}(s)$  and output voltage  $G_{v_{Cf}}(s)$  contains the right-half-plane (RHP) zeroes. With RHP zeroes, the expected voltage falls before rising to the reference when the step increase of control command is given [27]. This nonminimum phase system exhibits a worse dynamic response and causes oscillation. Usually, the inner current loop is essential to deal with such an influence and to obtain the good response.

Fig. 23 shows the block diagram of dc-side closed-loop controller.  $C_{i}(z) C_{v_{C}}(z)$ , and  $C_{v_{Cf}}(z)$  are the typical digital PI controller with antiwindup correction expressed in (49).  $H_i$  and  $H_{vc}, H_{vcf}$  are the coefficients of current and voltage sampling units, respectively.  $(1 - e^{-T_s s})/s$  is zero-order hold.  $e^{-T_d s}$  is time delay.  $G_{i_{L}}(s)$ ,  $G_{v_{C}}(s)$ , and  $G_{v_{Cf}}(s)$  are the control to state variable transfer functions expressed in (46)–(48).  $G_{i_L}(s)$ is the minimum phase system transfer function. And the total phase delay is 90°. Therefore, the inner current regulator  $C_i(z)$ is easily designed to meet the bandwidth requirement.  $C_{v_{C,t}}(z)$ provides the guidance for controller parameters design for ac output voltage. Applying the formula for Mason's rule, the inner current closed-loop transfer function is derived as (50). Once the current loop is designed, it can be treated as a new power stage for the outer voltage loop design. The closed-loop transfer functions of capacitor voltage and filtered output voltage are derived as (51) and (52)

$$G_c(z) = K_p + K_i T_s \cdot \frac{z}{z-1}$$

(49)

$$T_{i_{L}}(s) = \frac{C_{i}(s) \cdot G_{i_{L}}(s)}{1 + H_{i} \cdot C_{i}(s) \cdot G_{i_{L}}(s)}$$

(50)

$$T_{v_{C}}(s) = \frac{C_{v_{C}}(s) \cdot T_{i_{L}}(s) \cdot G_{v_{C}}(s)}{G_{i_{L}}(s) + H_{v_{C}} \cdot C_{v_{C}}(s) \cdot T_{i_{L}}(s) \cdot G_{v_{C}}(s)}$$

(51)

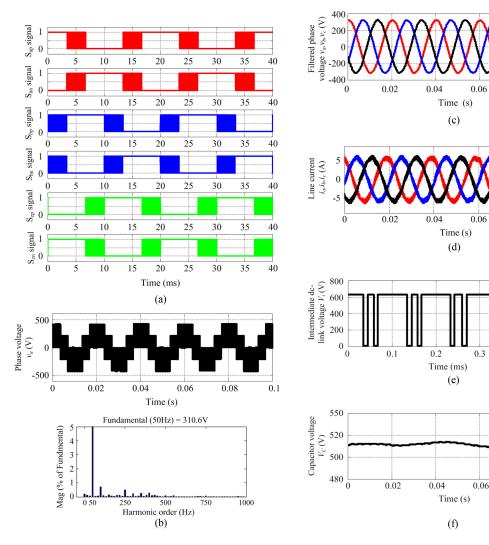

Fig. 24. Simulation results for Z-source inverter with IPWM + 1P ST. (a) Drive signal. (b) Output phase voltage and spectrum analysis. (c) Filtered output phase voltage. (d) Output line current. (e) Intermediate dc-link voltage. (f) Capacitor voltage.

$$T_{v_{C_{f}}}(s) = \frac{C_{v_{C_{f}}}(s) \cdot T_{i_{L}}(s) \cdot G_{v_{C_{f}}}(s)}{C_{i_{L}}(s) \cdot G_{i_{L}}(s) + H_{v_{C_{f}}} \cdot C_{v_{C_{f}}}(s) \cdot T_{i_{L}}(s) \cdot G_{v_{C_{f}}}(s)}.$$

(52)

# VI. SIMULATION AND EXPERIMENT VERIFICATION

Numerical simulations using MATLAB/Simulink have been performed to verify IPWM + 1P ST and theoretical analysis. The main circuit parameters are:  $V_{dc} = 300 - 400 \text{ V}, L =$ 8 mH,  $C_1 = C_2 = 330 \ \mu\text{F}$ ,  $L_f = 400 \ \mu\text{H}$ ,  $C_f = 25 \ \mu\text{F}$ ,  $R_{\text{Load}} =$ 60  $\Omega$ ,  $L_{\text{load}} = 2$  mH. The switching time period  $T_s$  is 100  $\mu$ s. The output line frequency is  $f_{\text{line}} = 50$  Hz. The current/voltage ripple coefficients of inductor/capacitor for Z-source network are preset as  $\delta_L = 0.4, \, \delta_C = 0.0015$  under the maximum operation condition G = 2.1,  $i_L = 10$  A, and  $V_C = 600$  V. The cutoff frequency of low-pass filter in output side is set about 2 kHz ( $f_c = 1/5f_s$ ) to attenuate the switching frequency ripples.

Fig. 24 shows the captured waveforms of Z-source inverter with IPWM + 1P ST under the output reference voltage of  $\hat{v}_{ac} = 310$  V. According to (6) and (22), the voltage gain G = 1.56, and the capacitor voltage  $V_C = 514.6$  calculated in theory are identical to the simulation results. Compared with the existing PWM strategies, Z-source inverter with IPWM + 1P ST achieves the maximum voltage gain as well as minimum voltage stress and switching frequency of power devices.

0.3

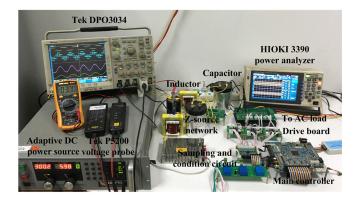

A laboratory prototype rated at 2.5 kW was built to confirm the IPWM strategy with Infineon power devices. Fig. 25 shows a photograph of the test platform. The main control board is designed based on DSP28335. The drive circuit of IGBT is designed with ACPL-330J based on the existing mature technology. A programmable dc power supply is arranged as the dc source to simulate the V - I characteristics of fuel cells and solar arrays. A Y-type three-phase RL load is connected to the ac side of the inverter. HIOKI 3390 power analyzer simultaneously measures the input dc power and ac output power to perform efficiency analysis. The time duration of each switching instant is precalculated in DSP28335. The conditioning board performs logic operations to generate gate signals of power devices according to the requirement of

0.08

0.08

0.4

0.08

0.1

0.1

0.5

0.1

Fig. 25. Z-source inverter test platform.

TABLE V

Specifications for the Experimental Prototype

| Switching device      | Front-end diode $S_{ap}, S_{an}, S_{bp}, S_{bn}, S_{cp}, S_{cn}$ | DIODE (IDP30E120)<br>IGBT(IGW25N120) and<br>DIODE(IDP18E120) |

|-----------------------|------------------------------------------------------------------|--------------------------------------------------------------|

| Passive components    | L                                                                | 8 mH                                                         |

|                       | $C_1$ and $C_2$                                                  | $330 \mu\text{F}$                                            |

| Three-phase EMI filer | $L_f$                                                            | $400 \mu \text{H}$                                           |

|                       | $C_{f}$                                                          | $35 \mu F$                                                   |

| Three-phase RL load   | $R_{1 o a d}$                                                    | $40 - 300 \Omega$                                            |

|                       | $L_{\rm load}$                                                   | 2 mH                                                         |

| Switching time period | $T_s$                                                            | 100 µ s                                                      |

| Current sensor        | $H_i$                                                            | 0.1                                                          |

| Voltage sensor        | $H_{\rm vc}$ and $H_{\rm vcf}$                                   | 0.01                                                         |

the output voltage vector. The specifications for the experimental prototype are listed in Table V. The key parameters of closed-loop controllers are  $G_{i_L}(z) = 0.11 + 0.0035 \cdot z/(z-1)$ ;  $G_{v_C}(z) = 0.06 + 0.012 \cdot z/(z-1)$ ;  $G_{v_Cf}(z) = 0.048 + 0.03 \cdot z/(z-1)$ .

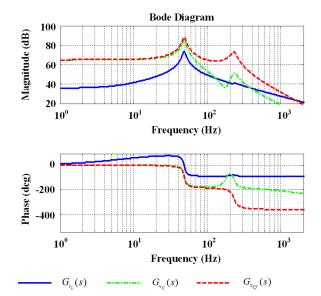

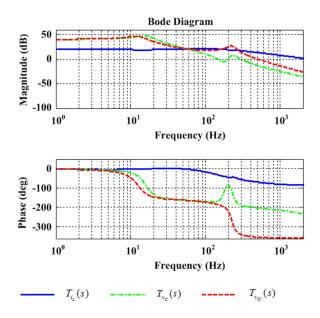

For Z-source inverter with IPWM + 1P ST, the inductor current in the impedance network inevitably contains 300 Hz low-frequency ripples for 50 Hz ac output. Fig. 26 shows the frequency characteristic of control to inductor current, intermediate capacitor voltage, and filtered output voltage. In order to suppress the undesired influence of low frequency ac components, the bandwidth of inner current loop is designed below 300 Hz. Fig. 27 shows the designed closed-loop frequency responses. The inner current loop is designed with 200 Hz bandwidth and  $45^{\circ}$  phase margin. The intermediate capacitor voltage loop and output voltage loop are designed with almost 25 Hz bandwidth and 30° phase margin, which is beneficial to reduce the voltage oscillatory.

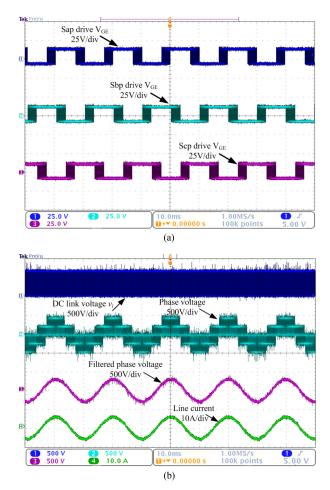

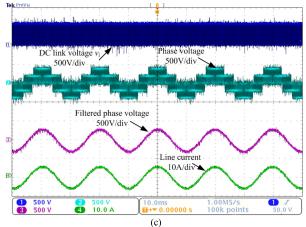

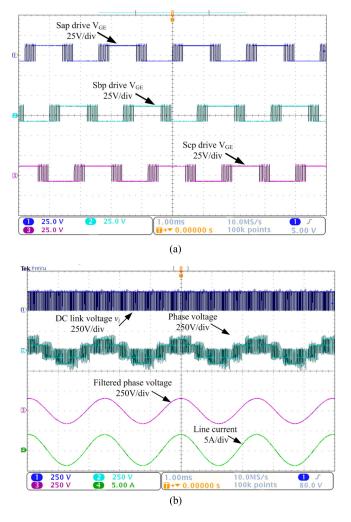

Fig. 28 shows the experiment results for Z-source inverter with IPWM + 1P ST under the output reference voltage of  $\hat{v}_{ac} = 310$  V when the input voltage  $V_{dc} = 300 - 400$  V. The maximum voltage gain of G = 2.07 can be obtained. Fig. 28(a) shows the voltage waveforms of gate signals for power devices  $(S_{ap}, S_{bp}, \text{ and } S_{cp})$ . During each sextant, the switches in the legs of  $v_{max}$  and  $v_{min}$  are fixed. Only switches in one phase leg of  $v_{mid}$  are commutating with PWM. Fig. 28(b) shows the captured waveforms of the intermediate dc-link voltage, the output phase

Fig. 26. Frequency characteristic of control to inductor current, intermediate capacitor voltage, and output voltage.

Fig. 27. Closed-loop frequency response of inductor current, intermediate capacitor voltage, and output voltage.

voltage before and after the filter, as well as the output current. By adjusting the ST to maintain the filtered output phase voltage is 220 V/50 Hz, the measured intermediate capacitor voltage is about 517.8 V, which is a little larger than the theoretical values of 514 V. This is due to the voltage drop and power loss of switches in the inverter bridge. Compared with existing PWM strategies, IPWM + 1P ST achieves the minimum intermediate dc-link capacitor voltage and equivalent switching frequency.

The maximum boost PWM strategy introduces six-time-linefrequency ripples in the dc-side inductor current and the capacitor voltage. Therefore, it is more suitable for 400–800 Hz medium frequency application of power supply system due to a relatively high output line frequency. Fig. 29 shows the captured waveforms for Z-source inverter using IPWM + 1P ST when the

Fig. 28. Z-source inverter with IPWM+1P ST ( $R_L = 60 \ \Omega$ ,  $f_{\text{line}} = 50 \text{ Hz}$ ). (a) Power device gate signals. (b) Intermediate dc-link voltage, output voltage, and current ( $V_{\text{dc}} = 300 \text{ V}$ ). (c) Intermediate dc-link voltage, output voltage, and current ( $V_{\text{dc}} = 400 \text{ V}$ ).

output phase voltage is 110 V/400 Hz, the dc source voltage is  $V_{\rm dc} = 200$  V, and the switching time period is  $T_s = 50 \ \mu s$ . The maximum voltage gain of G = 1.56 can be obtained. The measured intermediate capacitor voltage 261.3 V is quite consistent with the theoretical value 258 V calculated from (22).

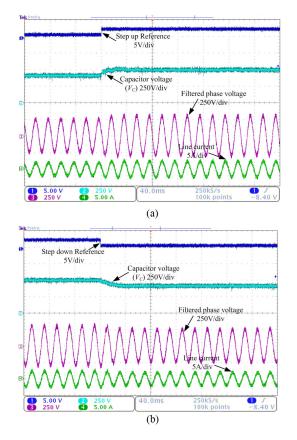

Fig. 30(a) and (b) shows the experimental results when the reference output voltage  $\hat{v}_{ac}^*$  has a step change from 250 V to 310 V

Fig. 29. Z-source inverter with IPWM + 1P ST ( $V_{\rm dc} = 200 \text{ V}, R_L = 40 \Omega, f_{\rm line} = 400 \text{ Hz}$ ). (a) Voltage waveforms of power device gate signals. (b) Intermediate dc-link voltage, output voltage, and current ( $V_{\rm dc} = 200 \text{ V}$ ).

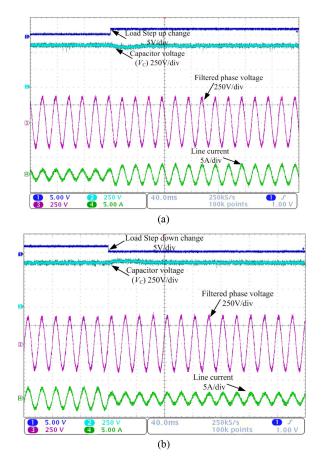

and back to 250 V, respectively. The controller is stable under steady state operation and the step change response is also fast with acceptable response time. With controller design shown in Fig. 21, the output three-phase voltage has good transient performance. The output three-phase voltage follows the reference when the intermediate capacitor voltage  $V_C = 413.5$  V achieves new steady state  $V_C = 514.4$  V. Fig. 31(a) and (b) shows the experimental results when the load resistance has a step change from  $R_L = 160 \Omega$  to  $R_L = 120 \Omega$  and back to  $R_L = 160 \Omega$ , respectively. The dc-side capacitor voltage and output ac voltage recover quickly.

The losses of power converter include semiconductor devices losses, passive components losses, controller and driver losses, etc. Among them, the semiconductor devices losses are the dominant part. IGBT losses consist of turn-on and turn-off switching losses besides conduction losses. DIODE losses include the reverse recovery losses and conduction losses because the turnon losses are small enough to be neglected [35]. The switching losses model of semiconductor device can be expressed as

Fig. 30. Dynamic responses of Z-source inverter under step change of output voltage reference ( $V_{\rm dc} = 300$  V,  $R_L = 120 \Omega$ ). (a) Step up 250–310 V. (b) Step down 310–250 V.

follows [35]-[37]:

$$E_{\rm sw(on,off)} = (\alpha + \beta \cdot i_{\rm sw} + \gamma \cdot i_{\rm sw}^2) \frac{V_{\rm sw}}{V_{\rm ref}}$$

(53)

$$P_{\rm sw} = f_{\rm sw} \cdot (E_{\rm swon} + E_{\rm swoff}) \tag{54}$$

where  $V_{\rm sw}$  is the blocking voltage,  $i_{\rm sw}$  is the switched current,  $\alpha$ ,  $\beta$ ,  $\gamma$  are the device parameters from the datasheet, and  $V_{\rm ref}$  is the reference voltage under which device parameters are derived.

The conduction losses of the front-end diode and switches in the inverter bridge can be calculated by

$$P_{\text{con.dc}} = \frac{1}{T_s} \int_{t_1}^{t_2} v_{\text{con}} \cdot i_{\text{con}} dt$$

(55)

$$P_{\text{con_inv}} = \frac{1}{2\pi} \int_{\lambda_1}^{\lambda_2} d_{\text{con}} \cdot v_{\text{on}} \cdot i_{\text{con}} d\theta_r \qquad (56)$$

where  $v_{\rm con} = v_{\rm th} + ri_{\rm con}$  is the on-state voltage drop,  $v_{\rm th}$  is the threshold voltage, r is the on-state resistor,  $i_{\rm con}$  is the conduction current, and  $d_{\rm con}$  is the conduction duration.

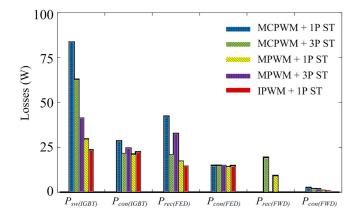

According to the power devices losses model, the switching losses and conduction losses of each power device can be calculated for theoretical analysis. Fig. 32 shows the losses distribution of Z-source inverter with different PWM strategies operating at normal condition as a reference. IGBT switching losses and front-end DIODE  $D_0$  reverse recovery losses occupy the main part. Therefore, the reduction of switching frequency

Fig. 31. Dynamic responses of Z-source inverter under step change of load resistance ( $V_{\rm dc} = 300 \text{ V}$ ,  $\hat{v}_{\rm ac} = 350 \text{ V}$ ). (a) Step change of  $R_L$  from 160  $\Omega$  to 120  $\Omega$ . (b) Step change of  $R_L$  from 120  $\Omega$  to 160  $\Omega$ .

Fig. 32. Theoretical analysis of losses distribution for Z-source inverter with different PWM strategies ( $V_{\rm dc} = 300$  V,  $\hat{v}_{\rm ac} = 311$  V,  $P_o = 2500$  W,  $T_s = 100 \ \mu$ s).

and voltage stress is of great importance for efficiency improvement. The conduction loss of free-wheeling diode is the minor part. All the PWM strategies only have a slight difference in the conduction losses of IGBT and  $D_0$ . This is because by using different PWM strategies, IGBT and  $D_0$  have almost the same average current stress in Figs. 15(b) and 17(b), respectively. MCPWM + 1P ST has the maximum IGBT switching losses due to a larger ST current compared with 3P ST method.

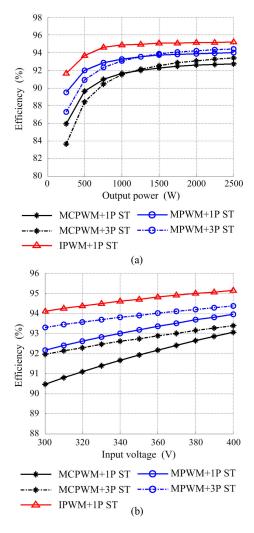

Fig. 33. Efficiency comparison of Z-source inverter with different PWM strategies. (a) Efficiency versus output power ( $V_{\rm dc} = 400$  V,  $\hat{v}_{\rm ac} = 311$  V,  $P_o = 250-2500$  W). (b) Efficiency versus input voltage ( $V_{\rm dc} = 300-400$  V,  $\hat{v}_{\rm ac} = 311$  V,  $P_o = 2500$  W).

Fortunately, for MCPWM + 1P ST in Fig. 5, MPWM + 1P ST in Fig. 7, and IPWM + 1P ST in Fig. 11, the ST interval is inserted at the instants of switching commutation between antiparalleled diode and IGBT. All the free-wheeling diodes in the inverter bridge achieve zero current turn OFF. Thus, free-wheeling diodes have almost no reverse recovery losses [34]. The turn-on losses of IGBT can be reduced too. Because the reduced switching frequency of IGBT and the front-end diode contributes to lowering power device losses, IPWM + 1P ST achieves the highest efficiency.

In order to quantify the improvement introduced by IPWM + 1P ST, the main circuit efficiency of Z-source inverter with different PWM strategies is measured under different output power and input voltage. Fig. 33 shows the efficiency comparison results of Z-source inverter operating at (a)  $V_{\rm dc} = 400$  V,  $\hat{v}_{\rm ac} = 311$  V,  $P_o = 250 - 2500$  W by the change of load resistance, and (b)  $V_{\rm dc} = 300 - 400$  V,  $\hat{v}_{\rm ac} = 311$  V,  $P_o = 2500$  W by the change of input voltage. The efficiency is increased with the decrease of voltage gain. Compared with existing PWM

Fig. 34. Current of  $S_{ap}$  during ST state for PWM strategies with 1P ST.

strategies, Z-source inverter with IPWM + 1P ST demonstrates best efficiency due to the reduced switching frequency and voltage stress of power devices.

## VII. CONCLUSION

This paper presents an IPWM strategy for Z-source inverter, which can minimize the voltage stress and switching frequency of power devices. Simulation and experiment results validate the theoretical analysis. Compared with existing PWM strategies, Z-source inverter with the IPWM demonstrates higher efficiency under full operation range of low voltage gain (1.27 - 2) application. However, the dc-side inductor current and capacitor voltage contain six-time-line-frequency ripples, which consequently require large size of the passive components when the output frequency is very low. Thus, it is also suitable for 400– 800 Hz medium frequency aircraft and vessel power supply system due to a relatively high output line frequency. Furthermore, the idea of IPWM strategy can be extended to other kinds of three-phase impedance network-based inverters.

## APPENDIX

1) Current Stress Derivation of IGBT and Free-Wheeling Diode

Because of the symmetry, each IGBT and free-wheeling diode in the inverter bridge has the same current stress. Thus, only IGBT  $S_{ap}$  and diode  $D_{an}$  are analyzed, for example.

(1) MCPWM + 1P ST

During ST interval,  $D_0$  is blocked. As shown in Fig. 34,  $i_{\text{Sap}}$  is  $i_{\text{dc_link}}$  minus  $i_{\text{bc}}$ .  $i_{\text{dc_link}}$  is  $2i_L$ .  $i_{\text{bc}}$  represents the sum of current across  $S_{\text{bp}}$  and  $S_{\text{cp}}$ , which depends on the current and switching states of phase b and c

$$\dot{a}_{\mathrm{Sap}} = i_{\mathrm{dc} \perp \mathrm{ink}}(\omega t) - i_{\mathrm{bc}}(\omega t) = 2i_L - i_{\mathrm{bc}}(\omega t)$$

(57)

$$i_{bc} = S_{bp} \cdot i_b(\omega t) + S_{cp} \cdot i_c(\omega t).$$

(58)

According to (57) and (58), ST current across  $S_{\rm ap}$  in different sextants can be derived as

$$i_{S1(ig)\_ST}(\omega t) = \begin{cases} 2i_L & \left(-\frac{\pi}{3} \le \omega t \le \frac{\pi}{3}\right) \\ 2i_L - i_b(\omega t) & \left(\frac{\pi}{3} \le \omega t \le \frac{\pi}{2}\right) \\ 2i_L - i_c(\omega t) & \left(-\frac{\pi}{2} \le \omega t \le -\frac{\pi}{3}\right) \end{cases}$$

(59)

From (59), the maximum instant current through  $S_{ap}$  occurs during ST interval  $i_{p,IGBT} = 2i_L$ . The ST interval  $d_{ST}$  is obtained from Table II.

During non-ST interval,  $S_{\rm ap}$  and  $D_{\rm an}$  conduct when  $i_a$  is positive  $(-\pi/2 \le \omega t \le \pi/2)$ . The conduction current is  $i_a$ . Thus, the maximum instant current through  $D_{\rm an}$  is peak value of load current  $i_{p,\rm FW,\rm DIODE} = \hat{i}_{\rm ac}$ . As shown in Fig. 5, the on-state interval of  $S_{\rm ap}$  and  $D_{\rm an}$  in a half line cycle can be derived as the following equations:

$d_{\text{Sap(IGBT)_NST}}(\omega t)$

$$= \begin{cases} V_{\operatorname{Sap}(\operatorname{San})}(\omega t) - \frac{d_{ST}(\omega t)}{6} & \left(\frac{\pi}{3} \le \omega t \le \frac{\pi}{2}\right) \\ V_{\operatorname{Sap}(\operatorname{San})}(\omega t) + \frac{d_{ST}(\omega t)}{6} & \left(-\frac{\pi}{3} \le \omega t \le \frac{\pi}{3}\right) \\ V_{\operatorname{Sap}(\operatorname{San})}(\omega t) - \frac{d_{ST}(\omega t)}{6} & \left(-\frac{\pi}{2} \le \omega t \le -\frac{\pi}{3}\right) \end{cases}$$

(60)

$d_{\text{San(Diode)}_{\text{NST}}}(\omega t)$

$$= \begin{cases} 1 - d_{\operatorname{Sap}(\operatorname{IGBT})\_\operatorname{NST}}(\omega t) - \frac{d_{\operatorname{ST}}(\omega t)}{2} & \left(-\frac{\pi}{3} \le \omega t \le \frac{\pi}{3}\right) \\ 1 - d_{\operatorname{Sap}(\operatorname{IGBT})\_\operatorname{NST}}(\omega t) - \frac{d_{\operatorname{ST}}(\omega t)}{6} & \left(\frac{\pi}{3} \le \omega t \le \frac{\pi}{2}\right) \\ 1 - d_{\operatorname{Sap}(\operatorname{IGBT})\_\operatorname{NST}}(\omega t) - \frac{d_{\operatorname{ST}}(\omega t)}{6} & \left(-\frac{\pi}{2} \le \omega t \le -\frac{\pi}{3}\right) \end{cases}$$

$$(61)$$

2) MPWM + 1P ST

For MPWM + 1P ST, the main difference from MCPWM + 1P is the periodically varied  $d_{ST}$  in (10).  $D_{an}$  is always turned OFF in the first sextant. Thus, the maximum instant current occurs at the beginning of the second sextant. It is half of load peak current  $i_{p\_FW\_diode} = 0.5\hat{i}_{ac}$ . Substituting (10) into (60) and (61), the key parameters for current stress analysis can be obtained.

3) IPWM + 1P ST

For IPWM + 1P ST, ST interval is inserted in phase a in the second sextant  $(\pi/3 \le \omega t \le 2\pi/3)$ . Thus, the maximum instant currents of IGBT and free-wheeling diode occur at the beginning of the second sextant.  $i_{p\_IGBT} = 2i_L - 0.5\hat{i}_{ac}$ .  $i_{p\_FW\_diode} = 0.5\hat{i}_{ac}$ .

(4) MCPWM + 3P ST

For MCPWM + 3P ST, during ST interval, all the switches in the inverter bridge are turned ON. Assuming the on-state resistors of each switch have the same value shown in Fig. 35, the current across  $S_{\rm ap}$  and  $S_{\rm an}$  meet

$$\begin{cases} i_{\text{Sap}}(\omega t) + i_{\text{San}}(\omega t) = \frac{4}{3}i_L\\ i_{\text{Sap}}(\omega t) - i_{\text{San}}(\omega t) = i_a(\omega t) \end{cases}$$

(62)

From (62), the ST current through  $S_{\rm ap}$  can be derived as

$$i_{\text{Sap}}(\omega t) = \frac{2}{3}i_L + \frac{1}{2}i_a(\omega t).$$

(63)

Fig. 35. Current of  $S_{\rm ap}$  during ST interval for MCPWM + 3P ST and MPWM+3P ST.

Fig. 36. Current analysis of  $D_0$  during non-ST interval.

From (63), the maximum instant current through IGBT during ST interval is

$$i_{p,\text{IGBT}} = \frac{2}{3}i_L + \frac{1}{2}\hat{i}_{\text{ac}}.$$

(64)

Seen from Fig. 35, during non-ST interval, the conduction current across  $S_{\rm ap}$  and  $D_{\rm an}$  is phase current  $i_a$ , but the conduction duration of  $S_{\rm ap}$  and  $D_{\rm an}$  decreases by  $d_{\rm ST}/2$  compared with conventional three-phase VSI

$$d_{\text{Sap}_{NST}}(\omega t) = V_{\text{Sap}(\text{San})}^{*}(\omega t) - \frac{1}{2}d_{\text{ST}}(\omega t)$$

(65)

$$d_{\text{Dan}_\text{NST}}(\omega t) = 1 - V^*_{\text{Sap}(\text{San})}(\omega t) - \frac{1}{2}d_{\text{ST}}(\omega t).$$

(66)

(5) MPWM + 3P ST

For MPWM + 3P ST, the key parameters of current stress analysis can be obtained by substituting (10) into (65) and (66).  $D_{\rm an}$  is always turned OFF in the first sextant. Thus, the maximum instant current occurs at the beginning of the second sextant  $i_{p,\rm FW,diode} = 0.5\hat{i}_{\rm ac}$ .

2) Current Stress Derivation of the Front-End Diode

As for Z-source inverter,  $D_0$  is conducting during non-ST interval and the equivalent circuit is shown in Fig. 36.  $i_{D0}$  can be expressed as  $2i_L - i_{dc,link}$ . In one switching time period,  $i_{dc,link}$  changes among zero and different load current

$$i_{D0_{\rm NST}}(\omega t) = i_L(\omega t) + i_C(\omega t) = 2i_L(\omega t) - i_{\rm dc\_link}(\omega t)$$

(67)

$$i_{\rm dc,link}(\omega t) = S_{\rm ap}(\omega t)i_a(\omega t) + S_{\rm bp}(\omega t)i_b(\omega t) + S_{\rm cp}(\omega t)i_c(\omega t).$$

(68)

C

In the first sextant,  $i_{D0}$  in different switching state is

$$i_{\rm FE(Diode)}(\omega t) = \begin{cases} 2i_L & (111\,000) \\ 2i_L - i_a(\omega t) & (100) \\ 2i_L + i_c(\omega t) & (110) \end{cases}$$

(69)

The corresponding duty ratio of different switching state is

$$\begin{cases} d_{(111,000)}(\omega t) = 1 - V_{\text{Sap}(\text{San})}^{*}(\omega t) & (111\,000) \\ + V_{\text{Scp}(\text{Scn})}^{*}(\omega t) - d_{\text{ST}}(\omega t) \\ d_{(100)}(\omega t) = V_{\text{Sap}(\text{San})}^{*}(\omega t) - V_{\text{Sbp}(\text{Scn})}^{*}(\omega t) & (100) \\ d_{(110)}(\omega t) = V_{\text{Sbp}(\text{Scn})}^{*}(\omega t) - V_{\text{Scp}(\text{Scn})}^{*}(\omega t) & (110) \end{cases}$$

(70)

With MCPWM + 1P ST and MCPWM + 3P ST, the peak current of  $D_0$  occurs in zero switching state, which is  $2i_L$ . With MPWM + 1P ST and MPWM + 3P ST, there is no zero switching state in non-ST interval. From (69), the peak current of  $D_0$  is

$$i_{P,\text{FE(Diode)}} = 2i_L - \frac{1}{2}i_{\text{ac}} = \left(\frac{3}{2} \cdot G - \frac{1}{2}\right)i_{\text{ac}}.$$

(71)

With different PWM strategies, the interval of active voltage vectors can be obtained from (70).

3) Passive Components Ripples Derivation

(1) MCPWM + 1P ST and MCPWM + 3P ST

#### A. Inductor Requirement

As shown in Fig. 10, during ST interval,  $V_L = V_C$  and  $i_L$  is increasing. And during non-ST interval,  $V_L = V_{dc} - V_C$  and  $I_L$  is decreasing. The average voltage across inductor in one switching time period is zero.

For MCPWM + 1P ST in Fig. 4 and MCPWM + 3P ST in Fig. 5, each ST interval is  $1/2d_{\rm st}T_s$  and  $1/6d_{\rm st}T_s$ ,, respectively. Thus, the inductor current ripples can be appropriately calculated based on  $d_{\rm ST}$  and  $V_C$

$$\Delta i_L = \frac{1}{L} \cdot V_C \cdot \frac{d_{ST}}{2} T_s \quad \text{For MCPWM} + 3P \text{ ST} \quad (72)$$

$$\Delta i_L = \frac{1}{L} \cdot V_C \cdot \frac{d_{\rm ST}}{6} T_s \quad \text{For MCPWM} + 1\text{P ST.} \quad (73)$$

Substituting  $V_C$  and  $d_{\rm ST}$  listed in Table II into (72) and (73),  $\Delta i_L$  can be rewritten as

$$\Delta i_L = \frac{\sqrt{3}}{8} \frac{\cdot (\sqrt{3}G - 2)G}{\sqrt{3}G - 1} \cdot \frac{V_{\rm dc}}{Lf_s} \quad \text{For MCPWM + 3P ST}$$

(74)

$$\Delta i_L = \frac{\sqrt{3}}{24} \frac{(\sqrt{3}G - 2)G}{\sqrt{3}G - 1} \cdot \frac{V_{\rm dc}}{Lf_s} \quad \text{For MCPWM + 1P ST.}$$

(75)

## B. Capacitor Requirement

As shown in Fig. 10, during ST interval, the discharging current of capacitor is  $i_L$

$$i_{C\_ST}(\omega t) = -i_L. \tag{76}$$

The charging current of capacitor during non-ST interval is  $i_L - i_{dc_1ink}$ , in which,  $i_{dc_link}$  changes among three-phase load current at different switching states.  $i_{C_NST}$  in the first sextant is expressed as

$$\sum_{\text{NST}} (\omega t) = i_L - i_{\text{dc}\_\text{link}} (\omega t)$$

$$= \begin{cases} i_L & (111\,000) \\ i_L - \hat{i}_{\text{ac}} \cos(\omega t) & (100) \\ i_L + \hat{i}_{\text{ac}} \cos\left(\omega t + \frac{2\pi}{3}\right) & (110) \end{cases} .$$

(77)

The average current across the capacitor in one switching time period is zero. From (76), the capacitor voltage ripples for MCPWM + 1P/3P ST can be calculated based on  $d_{ST}$  and  $i_L$

$$\Delta V_C = \frac{1}{C} \cdot i_L \cdot \frac{d_{\rm ST}}{2} T_s \quad \text{For MCPWM} + 3P \text{ ST} \quad (78)$$

$$\Delta V_C = \frac{1}{C} \cdot i_L \cdot \frac{d_{\rm ST}}{6} T_s \quad \text{For MCPWM} + 1P \text{ ST.} \quad (79)$$

Substituting  $i_L$  and  $d_{ST}$  in Table II into (78) and (79), the capacitor voltage ripples can be rewritten as

$$\Delta V_C = \frac{3}{16} \frac{(\sqrt{3}G - 2)G}{\sqrt{3}G - 1} \cdot \frac{\hat{i}_{ac}}{Cf_s} \quad \text{For MCPWM + 3P ST}$$

(80)

$$\Delta V_C = \frac{1}{16} \frac{(\sqrt{3G} - 2)G}{\sqrt{3G} - 1} \cdot \frac{\hat{i}_{ac}}{Cf_s} \quad \text{For MCPWM} + 1\text{P ST.}$$

(81)

Based on (76) and (77), the capacitor rms current ripples can be calculated as

$$I_{S\,\text{rms}}^{2} = \frac{6}{T_{\text{Line}}} \sum d(t) \cdot i_{C}^{2}(t)$$

$$= \frac{3}{\pi} \left[ \int_{0}^{\pi/3} \begin{pmatrix} d_{\text{ST}}(\omega t) \cdot (-i_{L})^{2} + d_{(111\,000)}(\omega t) \cdot (i_{L})^{2} \\ + d_{(100)}(\omega t) \cdot (i_{L} - \hat{i}_{\text{ac}}(\omega t))^{2} \\ + d_{(110)}(\omega t) \cdot (i_{L} + \hat{i}_{\text{ac}}\left(\omega t + \frac{2\pi}{3}\right)^{2} \end{pmatrix}^{2} d(\omega t) \right]$$

(82)

(2) MPWM + 1P ST, MPWM + 3P ST, and IPWM + 1P ST A. Inductor Requirement