LIS007307857B2

# (12) United States Patent Liu et al.

# (54) NON-ISOLATED DC-DC CONVERTERS WITH DIRECT PRIMARY TO LOAD CURRENT

(75) Inventors: Yan-Fei Liu, Kingston (CA); Sheng Ye,

Kingston (CA)

(73) Assignee: Queen's University at Kingston,

Kingston, Ontario (CA)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 11/504,775

(22) Filed: Aug. 16, 2006

(65) Prior Publication Data

US 2007/0103941 A1 May 10, 2007

## Related U.S. Application Data

- (63) Continuation of application No. 10/729,971, filed on Dec. 9, 2003, now Pat. No. 7,110,265.

- (60) Provisional application No. 60/431,740, filed on Dec. 9, 2002.

- (51) **Int. Cl.** *H02M 3/335* (2006.01)

See application file for complete search history.

# (56) References Cited

# U.S. PATENT DOCUMENTS

| 4,695,933 A  | 9/1987  | Nguyen et al.     |

|--------------|---------|-------------------|

| 5,875,103 A  | 2/1999  | Bhagwat et al.    |

| 6,163,466 A  | 12/2000 | Davila, Jr. et al |

| 6,388,898 B1 | 5/2002  | Fan et al.        |

# (10) Patent No.: US 7,307,857 B2

(45) **Date of Patent:** \*Dec. 11, 2007

| 6,392,902    | B1   | 5/2002  | Jang et al.                           |

|--------------|------|---------|---------------------------------------|

| 6,469,915    | B2   | 10/2002 | Huang et al.                          |

| 6,757,184    | B2*  | 6/2004  | Wei et al 363/71                      |

| 6,859,372    | B2 * | 2/2005  | Xu et al 363/17                       |

| 7,110,265    | B2*  | 9/2006  | Liu et al 363/16                      |

| 2002/0118000 | A1   | 8/2002  | Xu et al.                             |

| 2004/0246748 | A1*  | 12/2004 | $Xu\ et\ al.\ \dots\dots\dots 363/17$ |

### OTHER PUBLICATIONS

Yan-Fei Liu, and Paresh C. Sen, New Class-E DC-DC Converter Topologies with Constant Switching Frequency, IEEE Transactions on Industry Applications, vol. 32, No. 4, Jul./Aug. 1996, pp. 961-969, IEEE, USA.

(Continued)

Primary Examiner—Adolf Berhane

#### (57) ABSTRACT

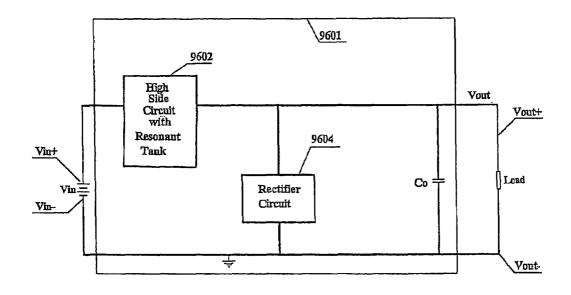

DC-DC converters have high side and rectifier circuits, and output capacitor. High side circuit connects between input voltage and output voltage, and has primary winding and auxiliary section that operate transformer properly. Auxiliary may have switches or combination of switches and capacitors. High side circuit converts electrical into magnetic energy through transformer primary, which is then transferred to output through rectifier circuit. It also transfers energy directly to output voltage. Converters have high efficiency, fast dynamic response and high current output. Converters can have large duty cycle and large input voltage and output voltage conversion ratio. High side circuit can be half-bridge, full-bridge or forward converter. Rectifier uses inductors on either side of the secondary, and diodes or synchronous rectifiers, to rectify output voltage. Multi-phase interleaved circuits utilize shared switches to reduce size. High side circuit can utilize resonant tank to decrease switching losses in auxiliary.

### 26 Claims, 74 Drawing Sheets

### OTHER PUBLICATIONS

Yan-Fei Liu, and Paresh C. Sen, A Novel Resonant Converter Topology for DC-to-DC Power Supply, IEEE Transactions on Aerospace and Electronic Systems, vol. 31, No. 4, Oct. 1995, pp. 1301-1313, IEEE, USA.

Yan-Fei Liu, and Paresh C. Sen, Source Reactance Lossless Switch (SRLS) for Soft-Switching Converters with Constant Switching Frequency, IEEE Transactions on Circuits and Systems—I: Fundamental Theory and Applications, vol. 43, No. 4, Apr. 1996, pp. 301-312, IEEE, USA.

Peng Xu, Fred C Lee, Jia Wei; The Coupled-Buck Converter for 12V VRM . . . ; VTIP Disclosure No. 01-002; Virginia Tech Intellectual Properties, Inc.; Blacksburg, Virginia.

Albert M. Wu, Seth R. Sanders; An Active Clamp Circuit for Voltage Regulation Module . . . ; IEEE Transactions On Power Electronics, vol. 16 No. 5 Sep. 2001 pp. 623-634.

Yuri Panov, Milan M. Jovanovic; Design Considerations for 12-V/1.5V, 50A Voltage Regulator . . . ; IEEE Transactions On Power Electronics, vol. 16 No. 6 Nov. 2001 pp. 776-783.

INTEL; VRM 9.1 DC-DC Converter Design Guidelines; Intel Corporation; Order No. 298646-001; Jan. 2002.

INTEL; VRM 9.0 DC-DC Converter Design Guidelines; Intel Corporation; Order No. 249205-004; Apr. 2002.

R.L. Steigerwald, "High frequency resonant transister DC-DC converters", IEEE Transactions on Industrial Electronics, vol. 31, pp. 181-191, May 1984.

F.S. Tsai, P. Materu, and F.C. Lee, "Constant-frequency, clamped-mode resonant converters", IEEE Transactions on Power Electronics, vol. 3, No. 4, pp. 460-473, Oct. 1988.

Y.F. Liu, P.C. Sen, "Source reactance lossless switch . . .", IEEE Transactions on Circuits and Systems—I, Fundamental Theory and Applications, vol. 43, No. 4, pp. 301-312, Apr. 1996.

Jia Wei et al; "A High Efficiency Topology for 12V VRM—Push-Pull Buck and Its Integrated Magnetics Implementations", APEC '02 Mar. 10, 2003, pp. 679-685, vol. 2, IEEE: NY, USA.

Peng Xu et al: "Investigation of Candidate Topologies for 12V VRM", APEC '02, Mar. 10, 2003, pp. 686-692, vol. 2, IEEE: NY, LISA

\* cited by examiner

Fig. 1 (Prior Art)

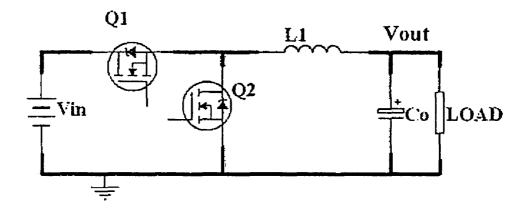

Fig. 2 (Prior Art)

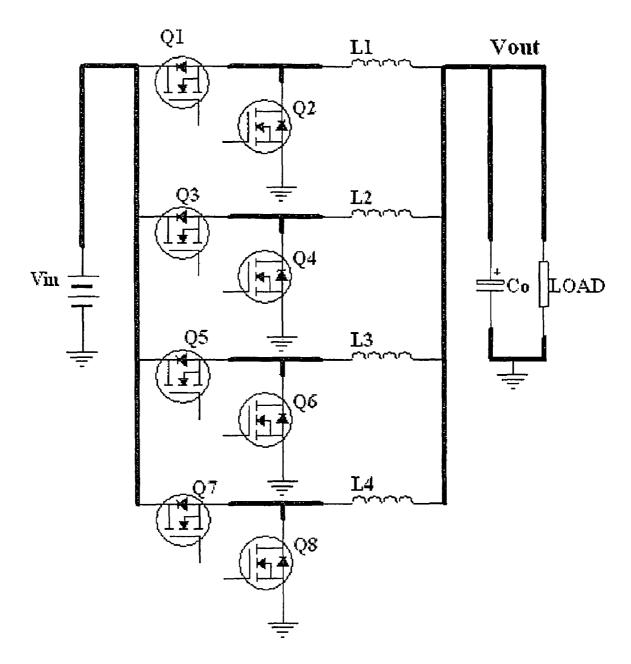

Fig. 3

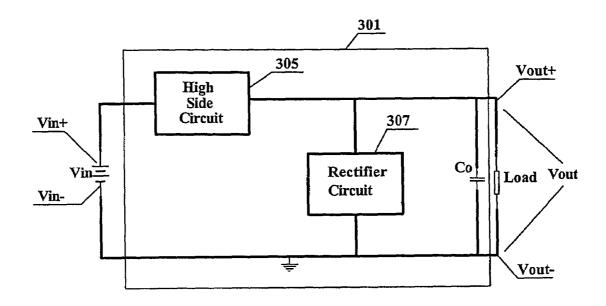

Fig. 4

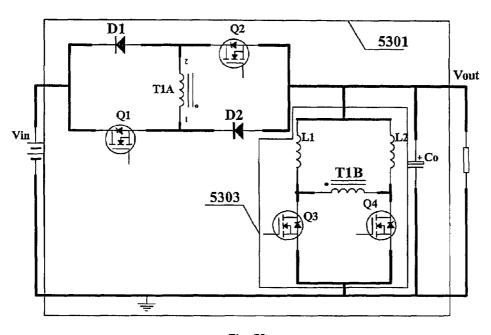

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig. 9

FIG. 10

Fig. 11

Fig. 12

Fig. 13

FIG. 14

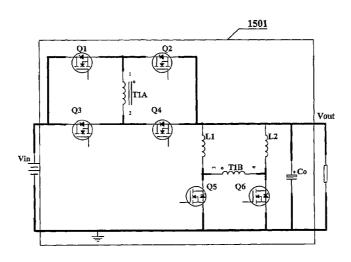

Fig. 15

Fig. 16

Fig. 17

Fig. 18

Fig. 19

Fig. 20

FIG. 21

Fig. 22

Fig. 23

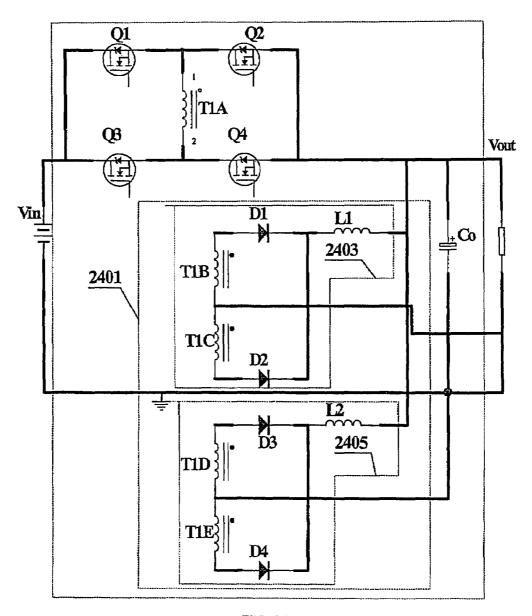

FIG. 24

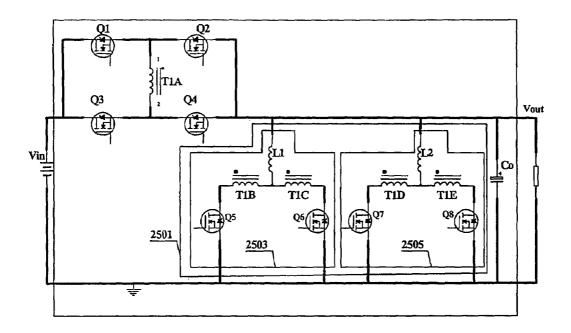

Fig. 25A

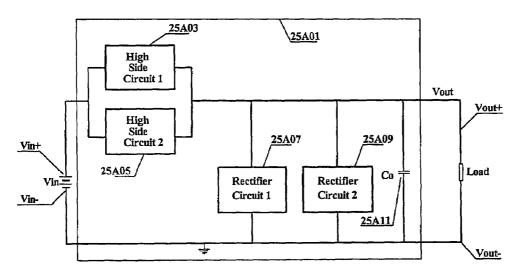

Fig. 25B

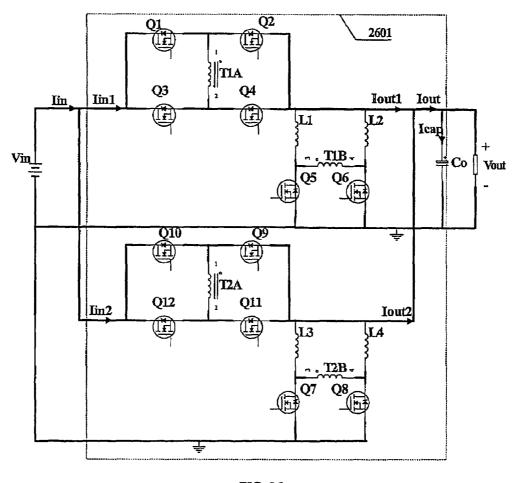

FIG. 26

Fig. 27

Fig. 28

Fig. 29

Fig. 32

Fig. 33

Fig. 34

Dec. 11, 2007

FIG. 36

Fig. 37A

Fig. 37B

FIG. 38A

Fig. 38B

FIG. 39

FIG. 41

Fig. 42

Fig. 43

FIG. 45

Fig. 46

Fig. 47

Fig. 49

FIG. 51

Dec. 11, 2007

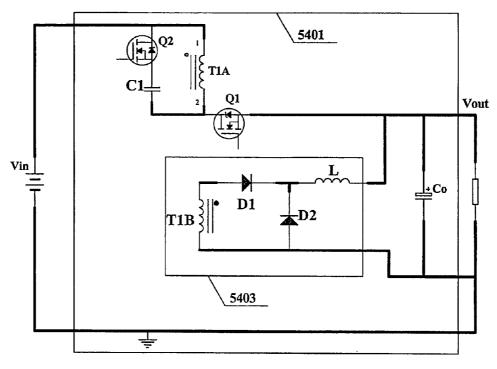

Fig. 52

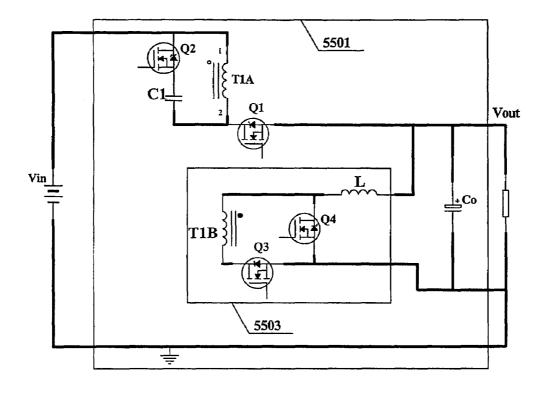

Fig. 53

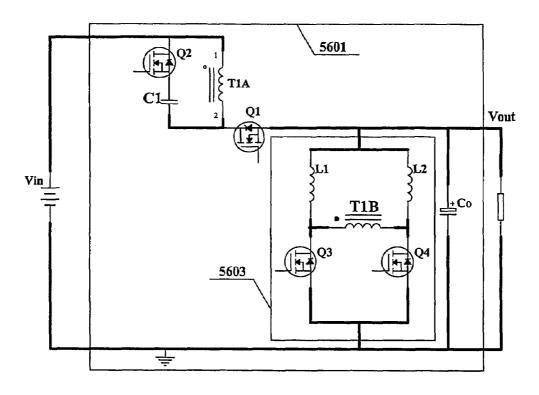

Fig. 54

Fig. 55

Fig. 56

Fig. 57

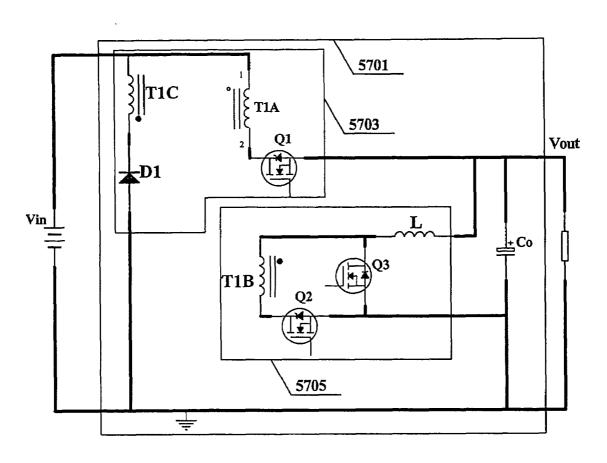

FIG. 58

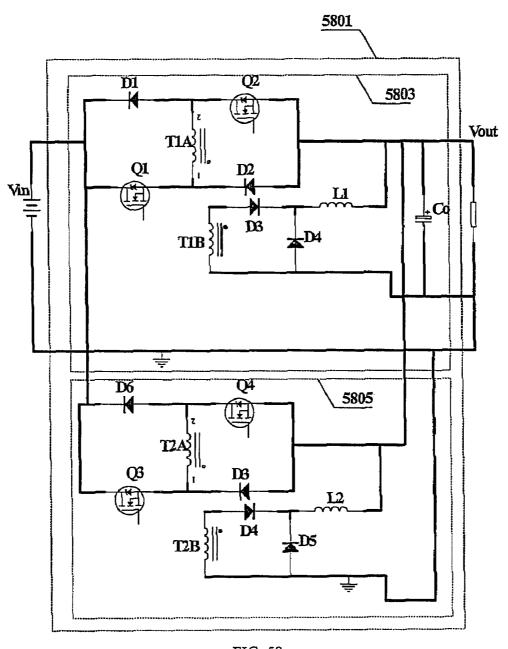

FIG. 60

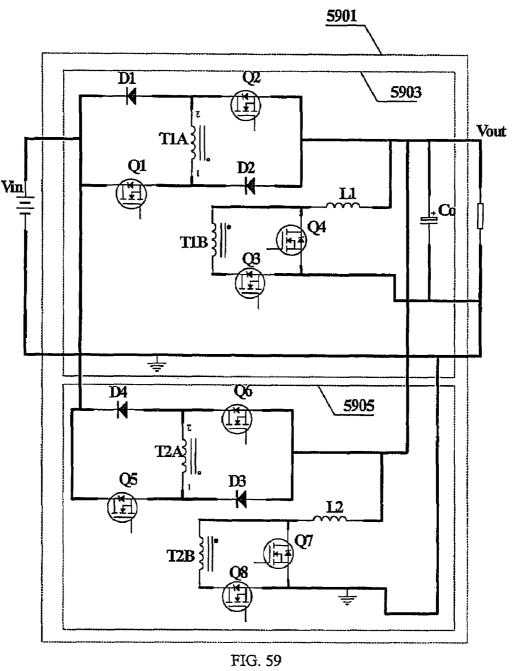

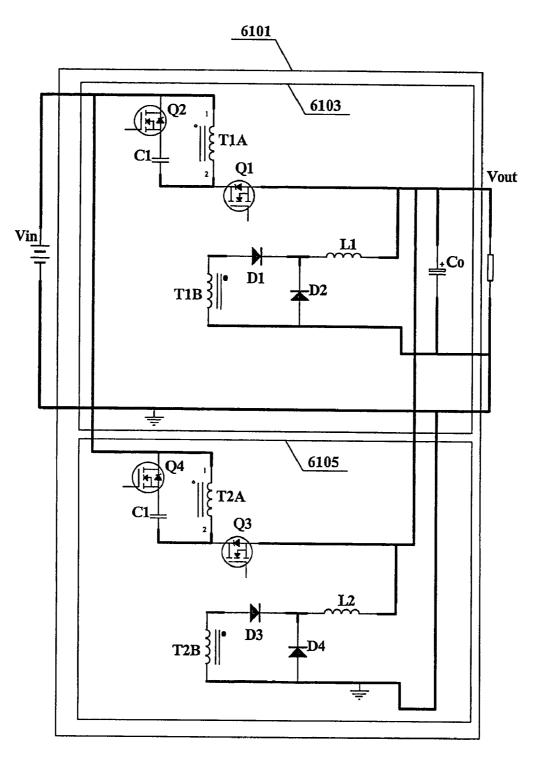

Fig. 61

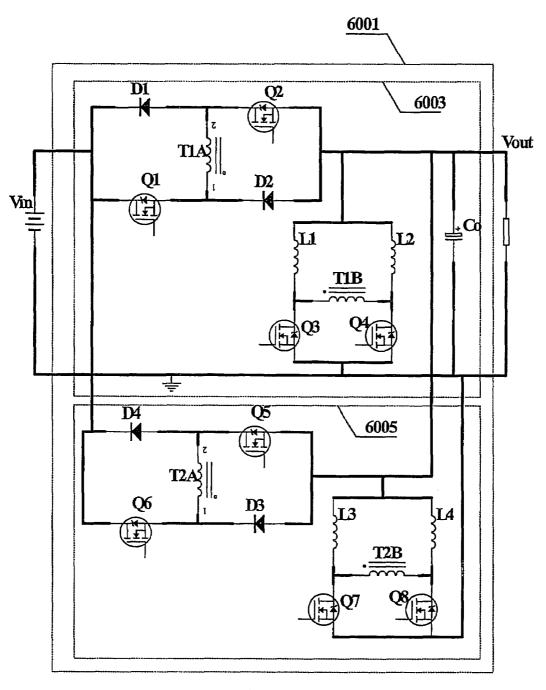

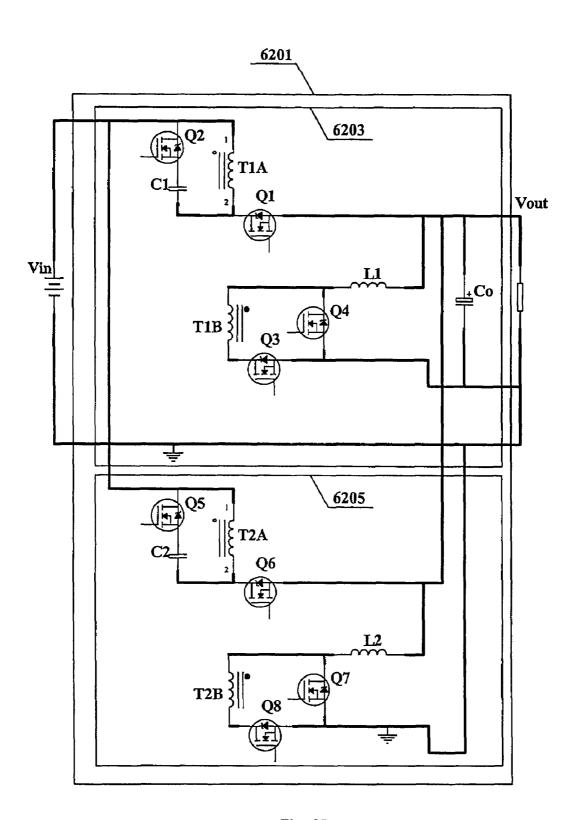

Fig. 62

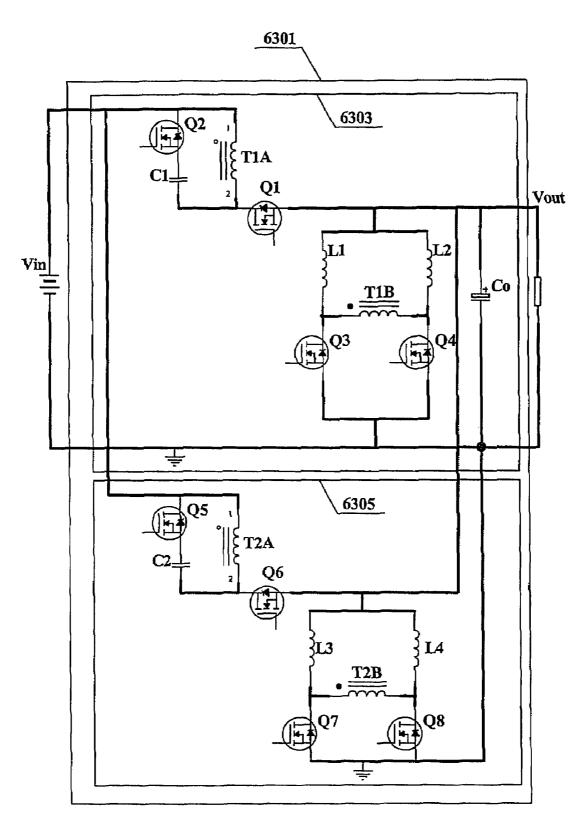

Fig. 63

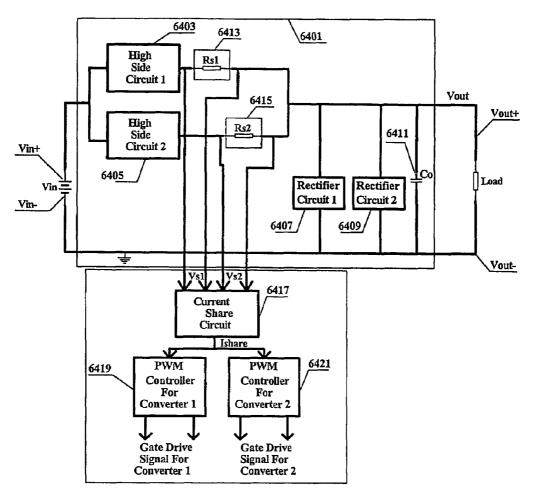

Fig. 64

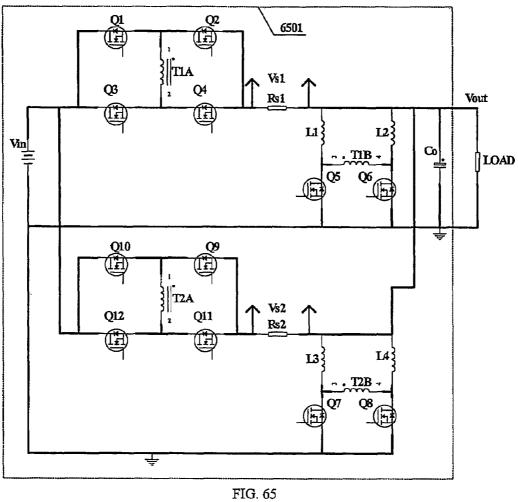

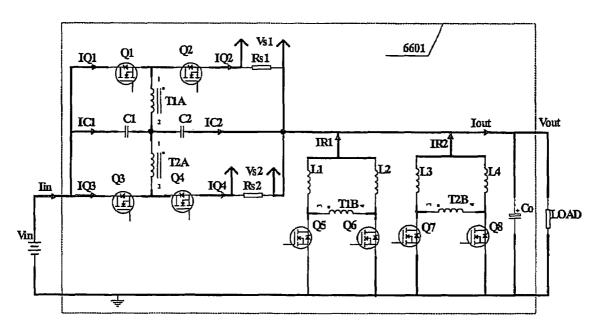

FIG. 66

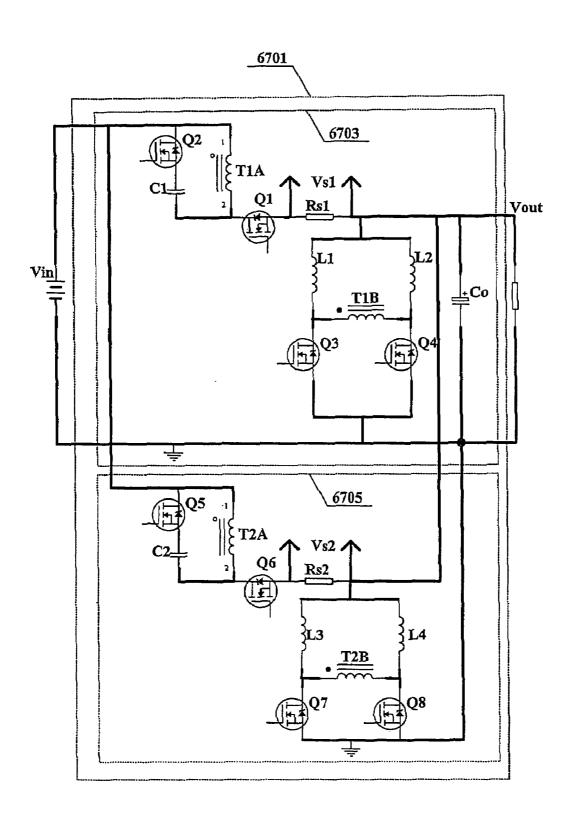

Fig. 67

FIG. 68A

FIG. 72

FIG. 74

Dec. 11, 2007

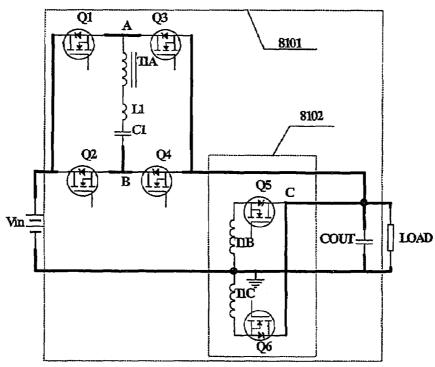

FIG. 81

FIG. 85

FIG. 93

## NON-ISOLATED DC-DC CONVERTERS WITH DIRECT PRIMARY TO LOAD CURRENT

## CROSS REFERENCE TO RELATED APPLICATIONS

This application claims priority from and is entitled to the benefit of the filing date of U.S. Provisional Patent Application No. 60/431,740 filed 9 Dec. 2002 under the same title 10 and by the same inventors.

### FIELD OF THE INVENTION

The invention relates to DC-DC converters. More par- 15 ticularly, it relates to such converters for low voltage central processing unit applications.

### BACKGROUND OF THE INVENTION

Computers are widely used both in our personal life and in our work. The heart of the computer is the central processing unit (CPU), which performs all the numerical calculation needed for today's ever demanding operation. In order to increase the calculation speed of the  $\widetilde{\text{CPU}}$ , and, thus  $^{25}$ the speed of the computer, the voltage required to power the CPU is becoming lower and lower. At the same time, the current that the CPU draws is becoming higher and higher. For example, the next generation CPU will require supply voltage of less than 1V and current of more than 100 A. The current view is that the required CPU supply voltage is from 0.8V to 1.6V for the next generation CPU.

For the CPU in a high-end server, the type of computer used to direct our Internet traffic and data transfer, the CPU's current requirement is even larger. The current for a server CPU could be up to 500 A.

As an example, in North America, power for a personal computer is typically drawn from a 120V AC wall outlet. This AC voltage is converted into a 12V DC voltage by an AC-to-DC converter. The 12V DC is distributed to a motherboard where the CPU is located. This 12V DC voltage cannot power the CPU directly. A DC-DC converter (often referred to as a voltage regulator module or VRM) is used to convert the 12V DC into the lower voltage required by the CPU. This power system architecture is currently preferred from a performance and cost point of view.

Another requirement of CPU powering is fast dynamic response. During a time when little calculation is required, the CPU will draw very low current. For the time when a lot 50 of calculation is required, the CPU will draw large current. The transition between the low current and large current is very fast. The current change rate can be as high as 10,000 A per microsecond. Therefore, the converter should have very fast dynamic response to meet this requirement.

If the response speed of the converter is not fast enough, the voltage across the CPU will have significant overshoot during the transition from large CPU current to low CPU current because an inductor is typically used in the converter. This voltage overshoot could cause damage to the CPU. Similarly, the voltage across the CPU will have significant undershoot during the transition from low CPU current to large CPU current. If the voltage is too low, the CPU may not operate properly.

be small in order to reduce the temperature rise of the semiconductors used to implement the converter.

Referring to FIG. 1, a Buck converter is typically used to convert incoming 12V into low output voltage such as 1.5V. The output voltage of a Buck converter is calculated as:

$V_{\text{out}}=D*V_{\text{in}}$

Where Vout is the output voltage and Vin is the input voltage. D is the duty cycle and is defined as:

Where Ton is the time period during which the top switch Q1 is conducting, and Ts is the switching period of Q1.

In order to achieve Vin=12V to Vout=0.8V conversion, the required duty cycle for Buck converter is D=0.8/12=7%. It is noted that a small duty cycle such as 7% is not optimal for the design and operation of a Buck converter when the switching time of the MOSFET ("metal-oxide semiconductor field-effect transistor") is considered. For example, for a typical MOSFET, the turn on time is around 50 ns and the turn off time is around 100 ns. This means that the MOSFET will be conducting for at least 150 ns regardless of the control signal. If we assume the switching frequency is 300 KHz, the switching period is 3.33 µs. The switching time of 150 ns is equivalent to 150 ns/3.33  $\mu$ s=4.5%. This means that we only have control of about 2.5% (7%-4.5%) of conducting time of the MOSFET. Considering the delay time of the controller, it is very difficult to design an actual implementation. The compromise is to reduce the switching frequency to a lower level, such as 200 KHz. However, lower switching frequency will also lower the dynamic response, which is a very important performance measurement for DC-DC converters.

In addition, operating at a very small duty cycle has another detrimental impact to the dynamic response. During the transition from low CPU current to high CPU current, the inductor current should be ramped up. This can be done by increasing the duty cycle from 7% (take the above example) to 100% (maximum). The duty cycle has 93% change, which is very beneficial to handle this transition. However, during the transition from high CPU current to low CPU current, the inductor current should be ramped down. The only way to achieve this is to reduce the duty cycle. Nevertheless, the duty cycle can only be reduced from 7% to 0%. The duty cycle has only 7% change, which results in poor dynamic response.

To improve the dynamic response, it is desirable to select higher switching frequency for the converter. It is also desirable for the converter to operate at around 50% duty

Referring to FIG. 2, in order to improve the dynamic response an interleaved Buck converter can be used, such as a four-phase interleaved Buck converter. By interleaving, the equivalent ripple frequency is 4 times the switching frequency of each phase. For example, if the switching frequency of each Buck converter is 200 KHz, the equiva-55 lent switching frequency for four-phase interleaved Buck converter will be 800 KHz. Another benefit of interleaving is that the ripple current through the output capacitor and input capacitor is also significantly reduced. However, each Buck converter still operates at very small duty cycle, which 60 is not desirable.

#### SUMMARY OF THE INVENTION

In a first aspect the invention provides a DC-DC converter In addition, the power loss for the converter should also 65 for use with a DC power source having a DC voltage across a first voltage source output and a second voltage source output and with a load. The converter includes an input for --- -----

accepting the DC voltage, the input having a first voltage input and a second voltage input. It also includes an output for outputting a converter DC voltage, the output having a first voltage output and a second voltage output. Furthermore it includes a high side circuit including a first primary winding of a first transformer and an auxiliary section, the high side circuit connected between the first voltage input and the second voltage output. It also includes a rectifier circuit having a first secondary winding of the first transformer, the rectifier circuit connected between the first voltage output and the second voltage output. There is also an output capacitor connected between the first voltage output and the second voltage output and across the rectifier circuit.

In this first aspect an output converter DC voltage 15 between the first voltage output and the second voltage output has the same polarity as a DC voltage input between the first voltage input and the second voltage input, The auxiliary section is for causing the first transformer to transfer power from the first primary winding to the first secondary winding and to operate without saturation. The high side circuit has a high side circuit output connected such that current flowing through the first primary winding is directed between the high side circuit output and the first voltage output. The rectifier circuit is for converting output of the first secondary winding into a one-direction waveform and converting the one-direction waveform into a DC voltage. The output capacitor is for filtering the converted DC voltage.

The auxiliary section may include switches for repeatedly 30 connecting and disconnecting the primary winding from the input, and allowing for resetting of the first transformer. The auxiliary section may have a combination of switches and capacitors. Alternatively, the auxiliary section may have four switches. Each switch may be a MOSFET.

Alternatively, the auxiliary section may have a first switch connected between a first side of the first primary winding and the first voltage input, a second switch connected between a second side of the first primary winding and the first voltage input, a third switch connected between the first side of the first primary winding and the high side circuit output, and a fourth switch connected between the second side of the first primary winding and the high side circuit output. Each switch may have an input for a gate drive signal for controlling the operation of the switch. The gate drive 45 signals may repeatedly turn on and turn off the first and fourth switch as well as turn on and turn off the second and third switch.

Alternatively, the auxiliary section may have a first switch connected between a first side of the first primary winding 50 and the first voltage input, a first capacitor connected between a second side of the first primary winding and the first voltage input, a second switch connected between the first side of the first primary winding and the high side circuit output, and a second capacitor connected between the 55 second side of the first primary winding and the high side circuit output. Each switch may have an input for a gate drive signal for controlling the operation of the switch. The converter may include gate drive signals adapted to repeatedly turn on and turn off the first switch and second switch, 60 whereby the first transformer can be reset from the capacitors. The capacitors may be large enough that the voltage across the capacitors will not change significantly during normal operation of the converter.

Alternatively, the auxiliary section may have a first switch 65 connected between a first side of the first primary winding and the first voltage input, a first diode connected between

a second side of the first primary winding and the first voltage input for forward conduction from the second side of the first primary winding to the first voltage input, a second switch connected between the second side of the first primary winding and the high side circuit output, and a second diode connected between the first side of the first primary winding and the high side circuit output for forward conduction from the high side circuit output to the first side of the first primary winding. Each switch may have an input for a gate drive signal for controlling the operation of the switch. The converter may have gate drive signals adapted to repeatedly turn on and turn off the first switch and second switch, whereby the first transformer can be reset by current flowing through the first and second diodes.

Alternatively, the auxiliary section may have a first side of the first primary winding connected to the first voltage input, the first switch connected between the first side of the first primary winding and the first side of the first capacitor, the second side of the first capacitor connected between the second side of the first switch and the second side of the first primary winding, a second switch connected between the second side of the first primary winding and the high side circuit output. Each switch may have an input for a gate drive signal for controlling the operation of the switch. The converter may have gate drive signals adapted to repeatedly turn on the first switch, while turning off the second switch, and turn off the first switch, while turning on the second switch, whereby the first transformer can be reset from the first capacitor.

The rectifier circuit may have a combination of inductors and switches, wherein the switches are for converting alternating voltage in the first secondary winding into pulsating one-direction voltage and the inductors are for converting pulsating one-direction voltage into DC voltage. Alternatively, the rectifier circuit may have a combination of inductors and diodes, wherein the diodes are for converting pulsating alternating voltage in the first secondary winding into pulsating one-direction voltage and the inductors are for converting pulsating one-direction voltage into DC voltage.

Alternatively, the rectifier circuit may have a first rectifier switch connected between the second voltage output and a first side of the first secondary winding, a second rectifier switch connected between a second side of the first secondary winding and the second voltage output, a first inductor connected between the first side of the first secondary winding and the first voltage output, and a second inductor connected between the second side of the first secondary winding and the first voltage output. Each switch may have an input for a gate drive signal for controlling the operation of the switch. The converter may have gate drive signals adapted to switch the first and second rectifier switches to convert bi-directional AC voltage at the first secondary winding into one-direction pulsating voltage.

Alternatively, the rectifier circuit further may have a first rectifier switch connected between the second voltage output and a first side of the first secondary winding, a second rectifier switch connected between a second side of the first secondary winding and the second voltage output, and a first inductor connected between the first side of the first secondary winding and the first voltage output not in series with the second rectifier switch.

Alternatively, the rectifier circuit may have first and second rectifier diodes and a first inductor, and the first diode is connected between a first side of the first secondary winding and the first inductor, and the inductor is further connected between the first diode and the first voltage output, for forward conduction from the secondary winding

through the inductor, and the second diode is connected between (a) a point between the second side of the first secondary winding and the second voltage output and (b) a point between the first inductor and first diode, also for forward conduction from the secondary winding through the 5 inductor. The first and second diodes, the first secondary and second secondary windings and the inductor may be within a first rectifier section, and the rectifier circuit also includes a second rectifier section similar to the first rectifier section, and the first and second rectifier sections are connected in parallel with one another and with the output capacitor and the output

Alternatively, the rectifier circuit may have a second secondary winding, first and second rectifier diodes and a first inductor, and a second side of the first secondary 15 winding is connected to a first side of the second secondary winding and the second voltage output, and the first diode is connected between a first side of the first secondary winding and the first inductor, and the inductor is further connected between the first diode and the first voltage output, for 20 forward conduction from the secondary winding through the inductor, and the second diode is connected between (a) a point between a second side of the second secondary winding and (b) a point between the first inductor and first diode, also for forward conduction from the secondary winding 25 through the inductor. The first and second rectifier switches, the first secondary and second secondary windings and the inductor may be within a first rectifier section, and the rectifier circuit further comprises a second rectifier section similar to the first rectifier section, and the first and second 30 rectifier sections are connected in parallel with one another and with the output capacitor and the output.

Alternatively, the rectifier circuit may have a second secondary winding, first and second rectifier switches and a first inductor, and a second side of the first secondary 35 winding is connected to a first side of the second secondary winding and the inductor which is further connected to the first voltage output, and the first rectifier switch is connected between a first side of the first secondary winding and the second voltage output, and the second rectifier switch is 40 connected between a second side of the second secondary winding and the second voltage output. The first and second rectifier switches, the first secondary winding and the first and second inductors may be within a first rectifier section, and the rectifier circuit also includes a second rectifier 45 section similar to the first rectifier section, and the first and second rectifier sections are connected in parallel with one another and with the output capacitor and the output.

The converter may have a second converter similar to the first converter, wherein the two converters are connected in 50 parallel with one another at their respective inputs and outputs. The output capacitors of the two converters may be combined as a single physical capacitor. The two converters may have interleaved gate drive signals, whereby current ripple incoming to the output capacitor is reduced, allowing 55 for reduction in the size of the output capacitor.

The converter may have a second transformer and the high side circuit may have a second primary winding of the second transformer, and first and second second primary switches, wherein the first second primary switch is connected between the first voltage input and a first side of the second primary winding, and the second second primary switch is connected between the first side of the second primary winding and the high side circuit output, and a second side of the second primary winding is connected to 65 a side of the first primary winding, and the rectifier circuit may have a second rectifier circuit similar to and connected

6

in parallel with the first rectifier circuit, wherein the second rectifier circuit includes a second second rectifier secondary winding of the second transformer. The second primary switches may have input for gate drive signals for operating the second primary winding out of phase with the first primary winding.

The converter may have a second transformer and the high side circuit may have a second primary winding of the second transformer, and first and second second primary switches, wherein the first second primary switch is connected between the first voltage input and a first side of the second primary winding, and the second second primary switch is connected between the first side of the second primary winding and the high side circuit output, and a second side of the second primary winding is connected to a side of the first primary winding, and the rectifier circuit may have a second rectifier secondary winding, a second rectifier inductor and a second rectifier switch, wherein a first side of the second rectifier secondary winding is connected to a first side of the first secondary winding and the second rectifier switch is connected between a second side of the second secondary winding and the second voltage output, and the inductor is connected between the second side of the second secondary winding and the high side circuit output, not in series with the second rectifier switch. The second primary switches may have inputs for gate drive signals for operating the second primary winding out of phase with the first primary winding, and the first and second rectifier circuit have inputs for gate drive signals for operating the rectifier circuit secondary windings phase shifted from one another.

The converter may have a second transformer and a third transformer, and the high side circuit may have a second primary winding of the second transformer, and first and second second primary switches, wherein the first second primary switch is connected between the first voltage input and a first side of the second primary winding, and the second second primary switch is connected between the first side of the second primary winding and the high side circuit output, and a second side of the second primary winding is connected to a side of the first primary winding, and the rectifier circuit may have a second rectifier circuit and a third rectifier circuit each similar to and connected in parallel with the first rectifier circuit, wherein the second rectifier circuit includes a second second rectifier secondary winding of the second transformer and the third rectifier circuit includes a third third rectifier secondary winding of the third trans-

The second primary switches may have input for gate drive signals for operating the second primary winding out of phase with the first primary winding, and no additional drive components are added for the third primary winding, wherein the converter has gate drive inputs for operating the third primary winding partially in phase with the first primary winding and partially in phase with the second primary winding.

The first voltage input may be for accepting a DC potential that is positive when compared to a DC potential for acceptance by the second voltage input. The DC potential of the first voltage output may be positive when compared to the DC potential of the second voltage output.

The input voltage of the converter may be within a range of 10.8 volts DC to 13.2 volts DC, and the out put voltage is within a range of 0.8 volts DC to 1.6 volts DC.

The duty cycle of single phase and two-phase converters may be between 40% and 60%. The duty cycle may be

approximately 50%. The duty cycle of three-phase converters may be approximately 33-1/3%.

The converter may have a second high side circuit similar to the first high side circuit, connected in parallel with the first high side circuit, and a second rectifier circuit connected 5 in parallel with the first rectifier circuit. The converter may have inputs for drive signals to operate the first high side circuit and the first rectifier circuit out of phase with the second high side circuit and the second rectifier circuit, respectively. The converter may have gate drive signals for 10 operating the first high side circuit and the first rectifier circuit out of phase with the second high side circuit and the second rectifier circuit, respectively.

The converter may have a current sensor in series with the high side circuit. Current sensed at the current sensor may be 15 and Q2 for the embodiment shown in FIG. 6; for use in determining the timing of gate drive signals for operating the high side circuit. The current sensed at the current sensor may also be used to make current sharing between two or more parallel connected converters.

The output of the first secondary winding may be a 20 pulsating voltage and the one-direction waveform may be a one-direction voltage.

The high side circuit may have a resonant tank.

The resonant tank may have a first capacitor in parallel with the first primary winding and a first inductor in series 25 with the first primary winding between the first primary winding and the auxiliary section.

The resonant tank further may also have a second capacitor in series with the first inductor between the first primary winding and the auxiliary section.

The resonant tank may also have a second inductor in parallel with the first primary winding and the first capacitor.

The resonant tank may have a first inductor and a first capacitor in series with one another between the first primary winding and the auxiliary section. In this case, the rectifier circuit may have a duty cycle and the duty cycle may be altered to change the output voltage of the converter.

For a resonant tank converter, the rectifier circuit may have a full-bridge rectifier. In such case, switches within the rectifier circuit may be controlled by phase control to regulate output voltage.

The rectifier circuit may have a half-bridge rectifier.

Switches in the resonant tank converter may be controlled by switching frequency control to regulate output voltage. 45

The auxiliary section may be a full-bridge auxiliary section. In such case for a resonant tank converter, switches within the auxiliary section may be controlled by phase shift control to regulate output voltage.

In another aspect the invention provides a method of 50 operating a converter of the type described above including the steps of driving the auxiliary section to cause the first transformer to transfer power from the first primary winding to the first secondary winding, while at the same time driving the auxiliary section to cause the transformer to 55 FIG. 15; operate without saturation.

Other aspects of the invention, including other methods employing converters, will be evident from the figures and detailed description herein.

## BRIEF DESCRIPTION OF THE DRAWINGS

For a better understanding of the present invention and to show more clearly how it may be carried into effect, reference will now be made, by way of example, to the 65 accompanying drawings which show the preferred embodiment of the present invention and in which:

8

FIG. 1 is a schematic diagram of a Buck converter of known configuration;

FIG. 2 is a schematic diagram of a four-phase interleaved Buck converter of known configuration;

FIG. 3 is a schematic diagram of a non-isolated DC converter in accordance with a preferred embodiment of the present invention;

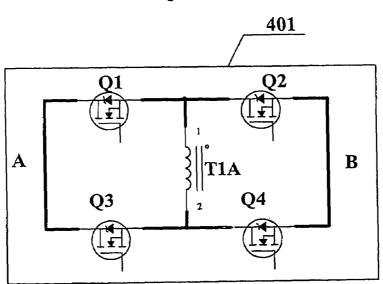

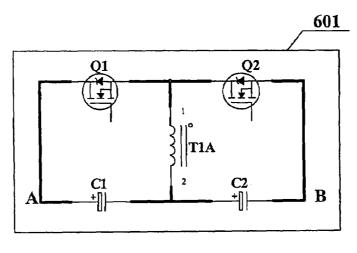

FIG. 4 is a schematic diagram of one embodiment of a high side circuit for the converter of FIG. 3;

FIG. 5 is a schematic diagram of gate drive signals for Q1 and Q2 for the embodiment shown in FIG. 4;

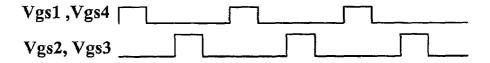

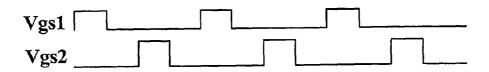

FIG. 6 is a schematic diagram of another embodiment of a high side circuit for the converter of FIG. 3;

FIG. 7 is a schematic diagram of gate drive signals for Q1

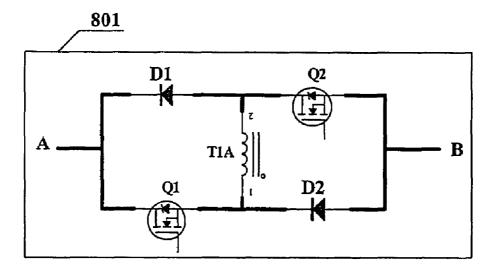

FIG. 8 is a schematic diagram of another embodiment of a high side circuit for the converter of FIG. 3 using two MOSFETs and two diodes;

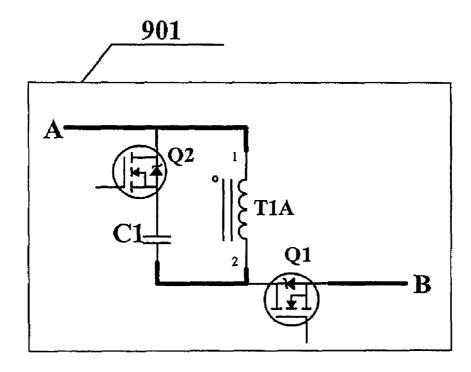

FIG. 9 is a schematic diagram of another embodiment of a high side circuit for the converter of FIG. 3;

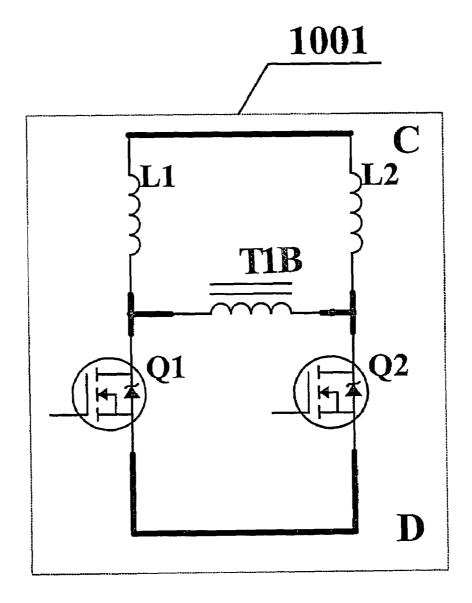

FIG. 10 is a schematic diagram of an embodiment of a rectifier circuit for the converter of FIG. 3 using one transformer winding and synchronous rectifiers;

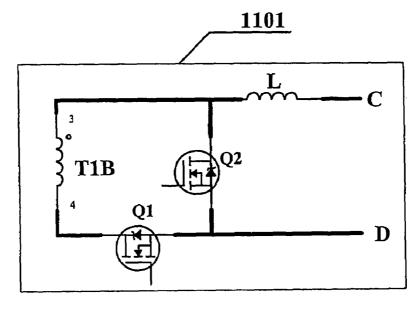

FIG. 11 is a schematic diagram of another embodiment of a rectifier circuit for the converter of FIG. 3 using one transformer winding and synchronous rectifiers;

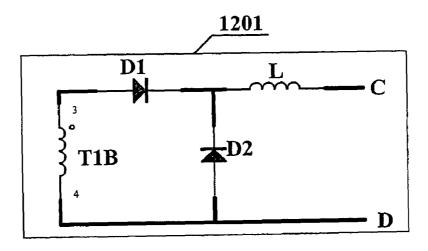

FIG. 12 is a schematic diagram of another embodiment of a rectifier circuit for the converter of FIG. 3 using one transformer winding and diodes;

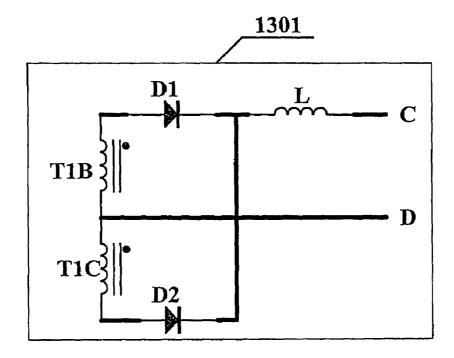

FIG. 13 is a schematic diagram of another embodiment of a rectifier circuit for the converter of FIG. 3 using two windings and two diodes;

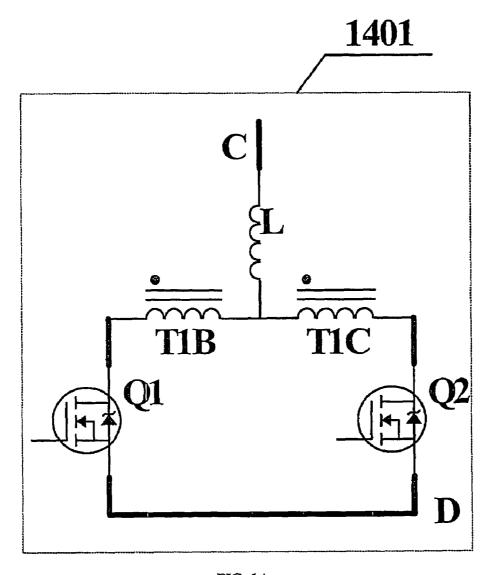

FIG. 14 is a schematic diagram of another embodiment of a rectifier circuit for the converter of FIG. 3 using two windings and synchronous rectifiers;

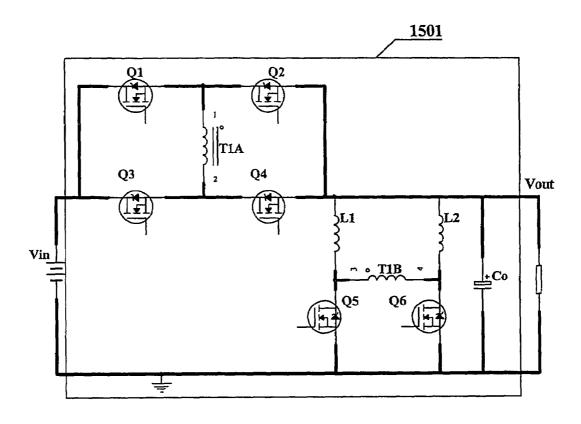

FIG. 15 is a schematic diagram of a non-isolated fullbridge DC converter embodiment of the converter of FIG. 3;

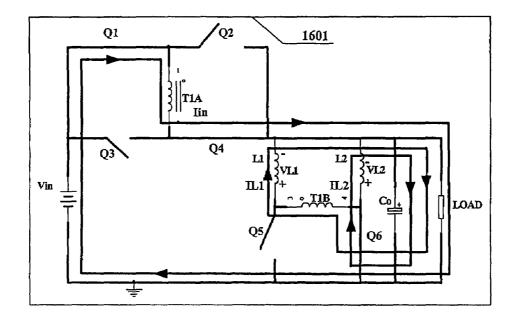

FIG. 16 is a schematic diagram of an equivalent circuit for the converter of FIG. 15 when Q1, Q4 and Q6 are on;

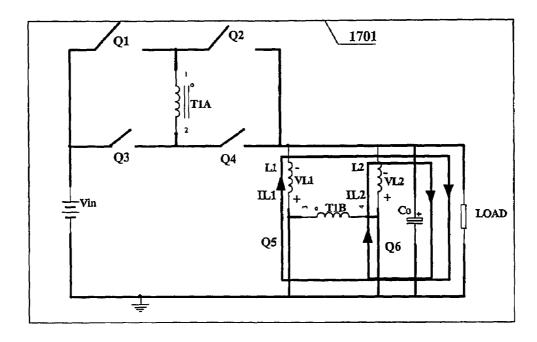

FIG. 17 is a schematic diagram of an equivalent circuit for the converter of FIG. 15 when Q1, Q2, Q3 and Q4 are off and Q5, Q6 are on;

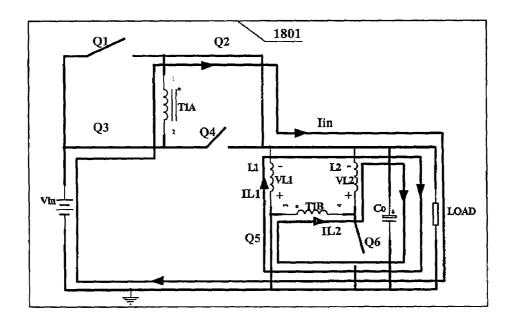

FIG. 18 is a schematic diagram of an equivalent circuit for the converter of FIG. 15 when Q2, Q3 and Q5 are on;

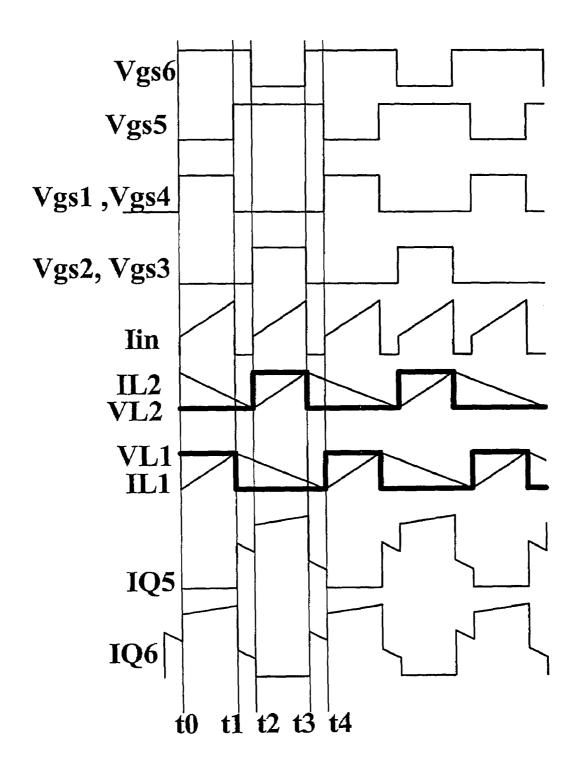

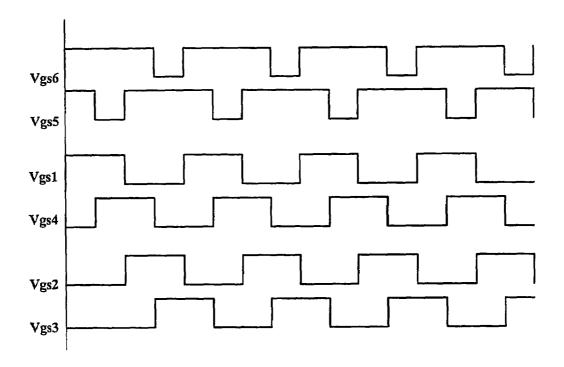

FIG. 19 is a graphic illustration of certain waveforms used with the non-isolated full-bridge DC converter of FIG. 15 for regular PWM (pulse width modulated) gate drive;

FIG. 20 is a graphic illustration of certain waveforms used with the non-isolated full-bridge DC converter of FIG. 15 for phase-shifted PWM gate drive signals for Q1, Q2, Q3, Q4, Q5 and Q6;

FIG. 21 is a schematic diagram of another non-isolated full-bridge DC converter embodiment of the converter of

FIG. 22 is a schematic diagram illustrating the use of synchronous rectifiers instead of diodes in the converter of FIG. 21;

FIG. 23 is a schematic diagram of a non-isolated full-60 bridge DC converter embodiment of the converter of FIG. 3 with two rectifier sections;

FIG. 24 is a schematic diagram of another non-isolated full-bridge DC converter embodiment of the converter of FIG. 3 with two rectifier sections;

FIG. 25A is a schematic diagram illustrating the use of synchronous rectifiers instead of diodes in the embodiment of FIG. 24;

- FIG. 25B is a schematic diagram of a two-phase interleaved non-isolated DC converter embodiment of the con-

- FIG. 26 is a schematic diagram of a two-phase interleaved non-isolated DC converter embodiment of the converter of 5 FIG. 3;

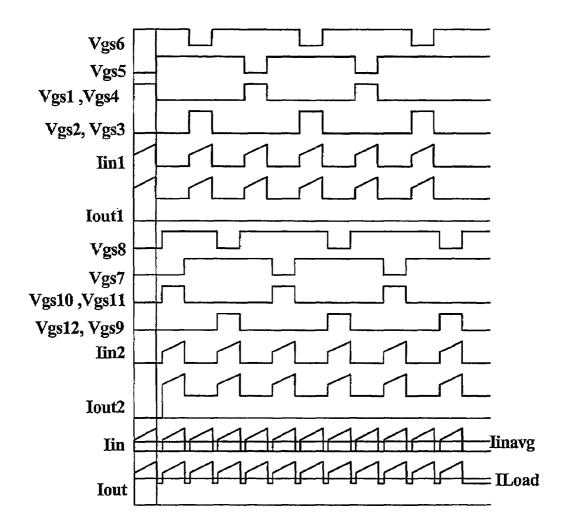

- FIG. 27 is a graphic illustration of certain waveforms used with the two-phase interleaved non-isolated full-bridge DC converter embodiment of FIG. 26 with duty cycle of 40%;

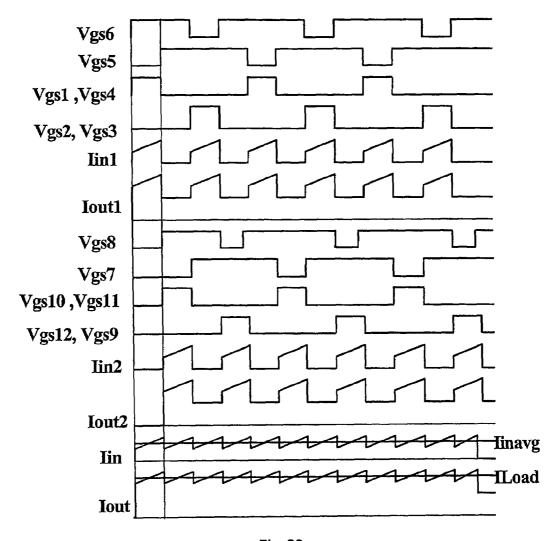

- FIG. 28 is a graphic illustration of certain waveforms used with the two-phase interleaved non-isolated full-bridge DC converter embodiment of FIG. 26 with duty cycle of 50%;

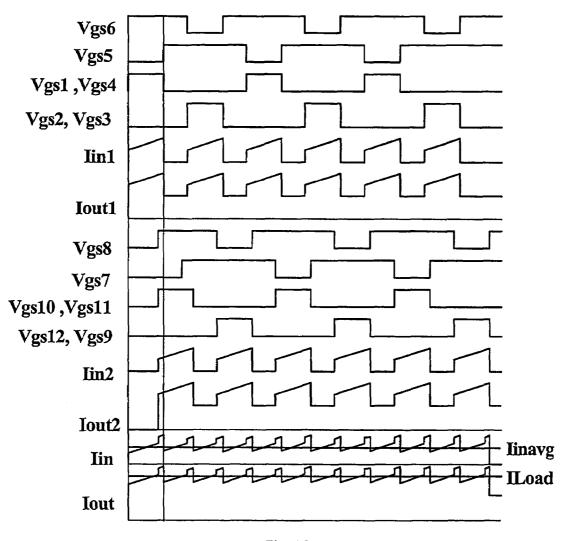

- FIG. 29 is a graphic illustration of certain waveforms used with the two-phase interleaved non-isolated full-bridge DC converter embodiment of FIG. 26 with duty cycle of 60%;

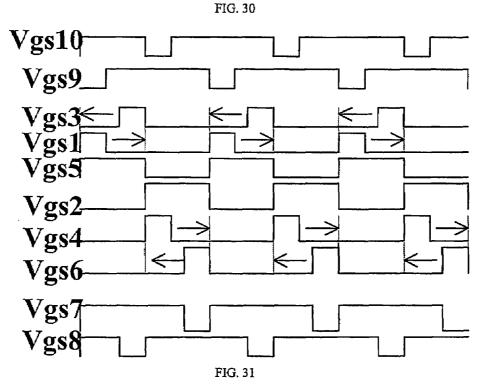

- FIG. 30 is a schematic diagram of a two-phase interleaved non-isolated full-bridge DC converter embodiment of the converter of FIG. 3 with a high side circuit shared switch;

- FIG. 31 is a schematic diagram of gate drive signals for the DC converter of FIG. 30;

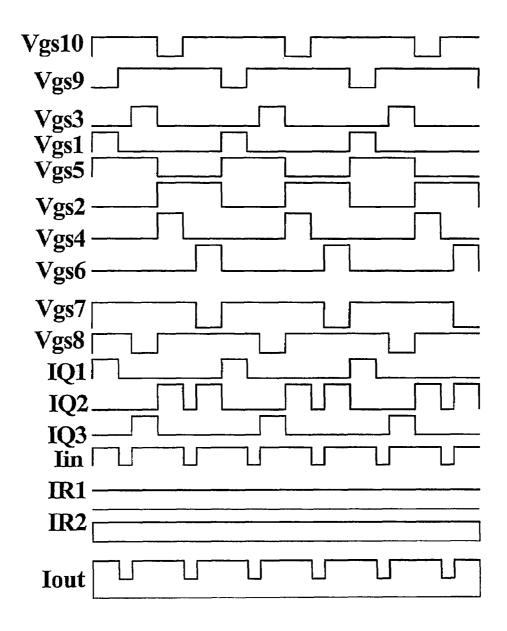

- FIG. 32 is a graphic illustration of certain waveforms used with the two-phase interleaved non-isolated full-bridge DC converter embodiment of FIG. 30 with duty cycle of 40%;

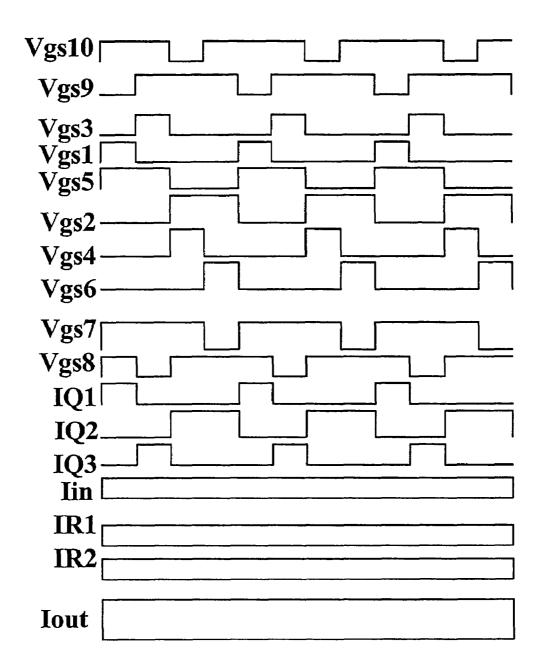

- FIG. 33 is a graphic illustration of certain waveforms used with the two-phase interleaved non-isolated full-bridge DC converter embodiment of FIG. 30 with duty cycle of 50%;

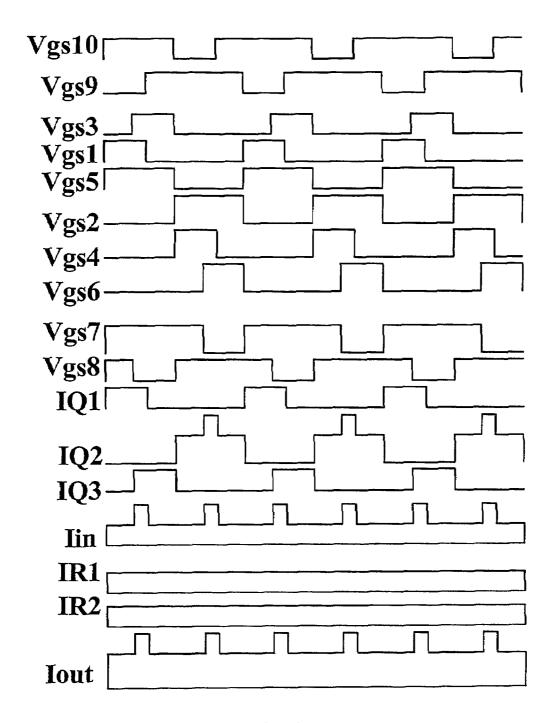

- FIG. 34 is a graphic illustration of certain waveforms used with the two-phase interleaved non-isolated full-bridge DC converter embodiment of FIG. 30 with duty cycle of 60%; 30

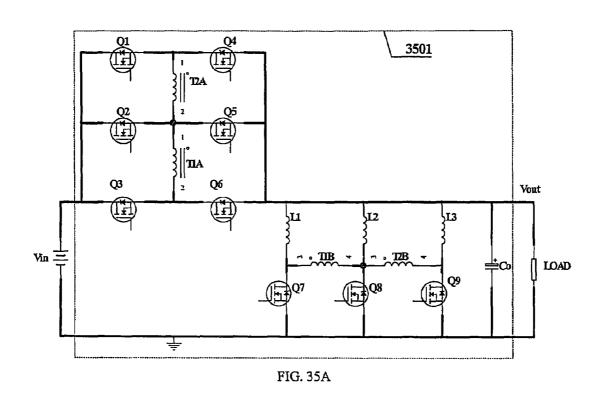

- FIG. 35A is a schematic diagram of a two-phase interleaved non-isolated full-bridge DC converter embodiment of the converter of FIG. 3 with high side circuit shared switch and rectifier circuit shared switch;

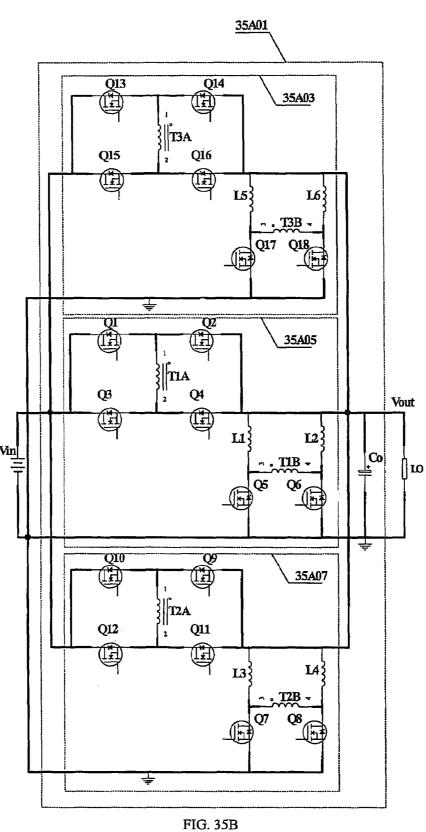

- FIG. 35B is a schematic diagram of a basic three-phase 35 interleaved non-isolated full-bridge DC converter embodiment of the converter of FIG. 3

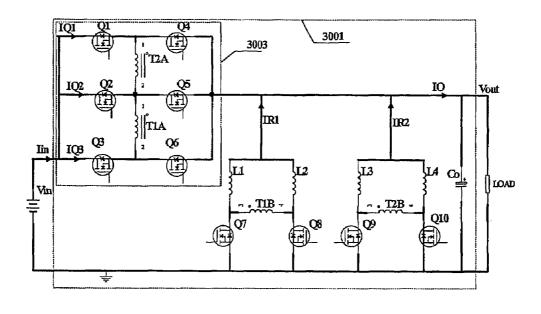

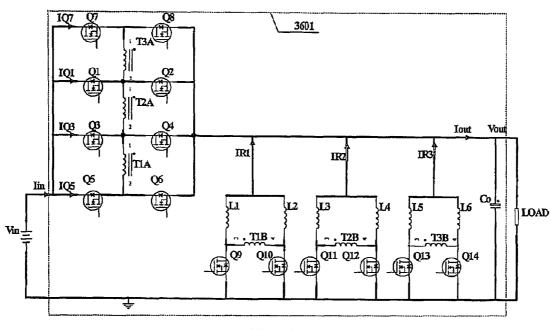

- FIG. 36 is a schematic diagram of a three-phase interleaved non-isolated full-bridge DC converter embodiment of the converter of FIG. 3 with primary shared switches;

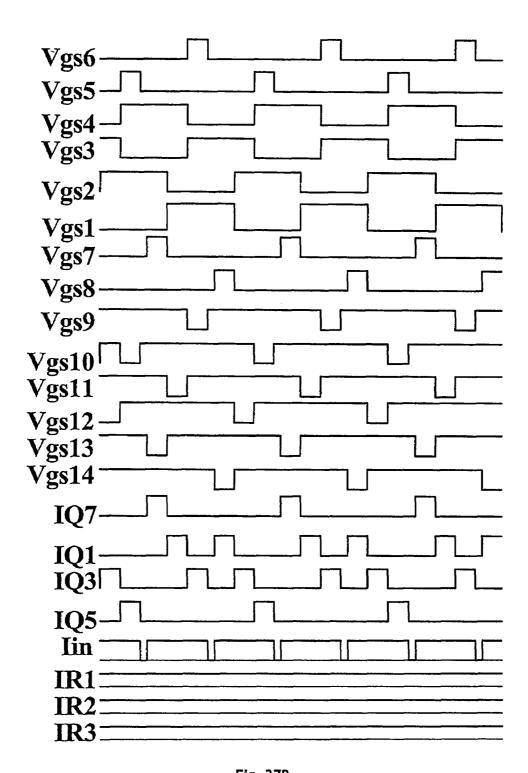

- FIG. 37A and FIG. 37B are each a graphic illustration of a gate drive scheme for the converter of FIG. 36 with a duty cycle of 30%;

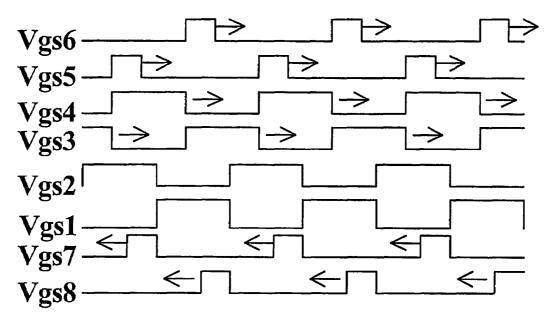

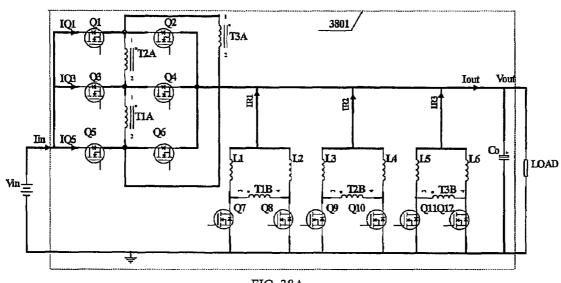

- FIG. 38A is a schematic diagram of a simplified threephase interleaved non-isolated full-bridge DC converter 45 embodiment of the converter of FIG. 3 with primary shared switches:

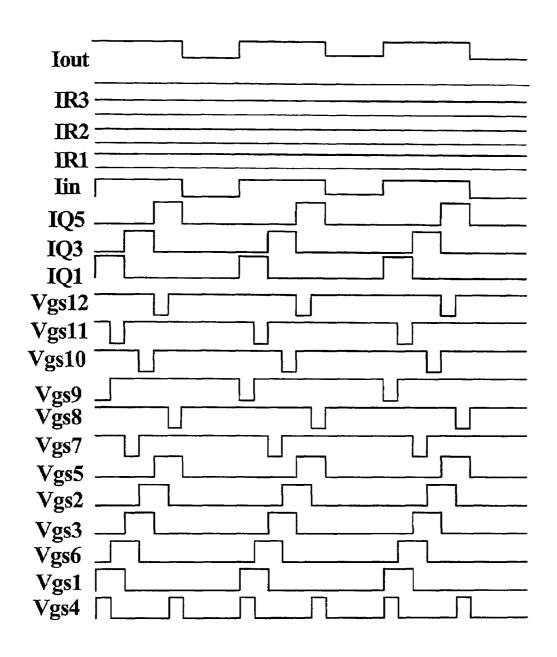

- FIG. 38B is a graphic illustration of one gate drive scheme for the converter shown in FIG. 38A.

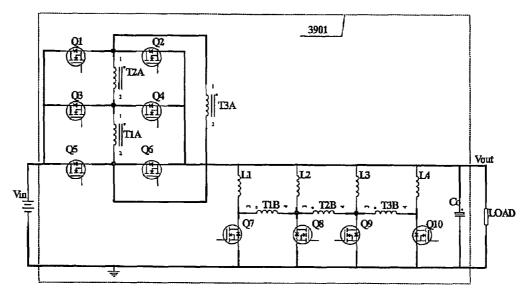

- FIG. 39 is a schematic diagram of a simplified three-phase interleaved non-isolated full-bridge DC converter embodiment of the converter of FIG. 3 with primary shared switches and rectifier circuit shared switch;

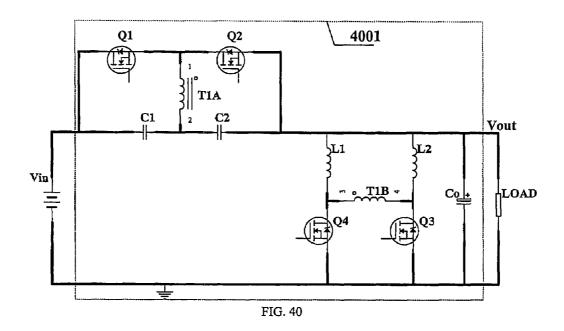

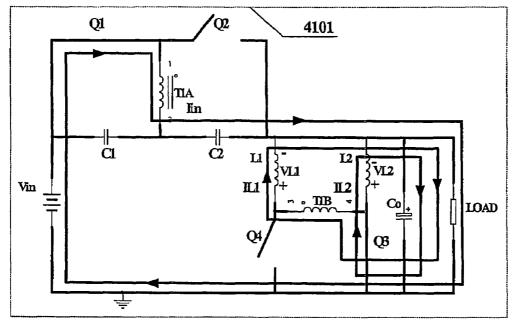

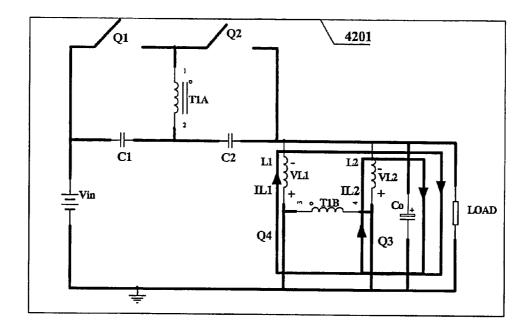

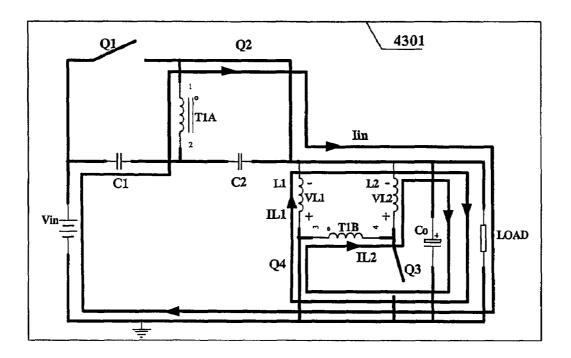

- FIG. 40 is a schematic diagram of a non-isolated halfbridge DC converter embodiment of the converter of FIG. 3;

- FIG. 41 is a schematic diagram of an equivalent circuit for the converter of FIG. 40 when Q1, Q4 and Q6 are on;

- FIG. 42 is a schematic diagram of an equivalent circuit for the converter of FIG. 40 when Q3 and Q4 are on;

- FIG. 43 is a schematic diagram of an equivalent circuit for the converter of FIG. 40 when Q2 and Q4 are on;

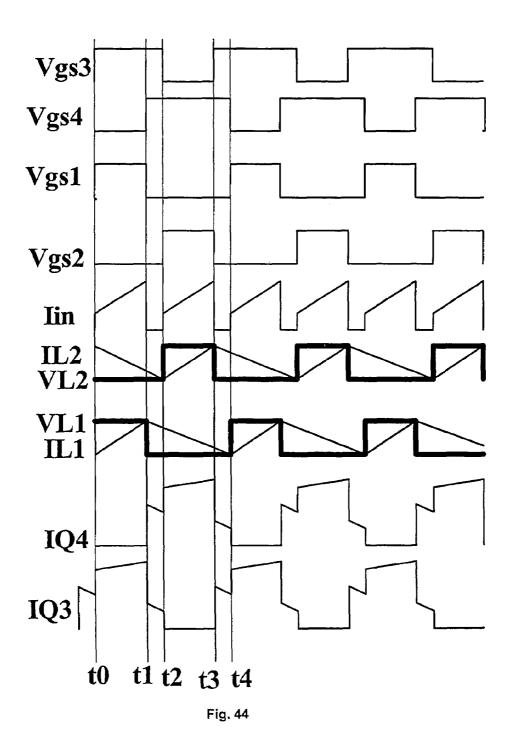

- FIG. 44 is a graphic illustration of certain waveforms for the half-bridge converter of FIG. 40;

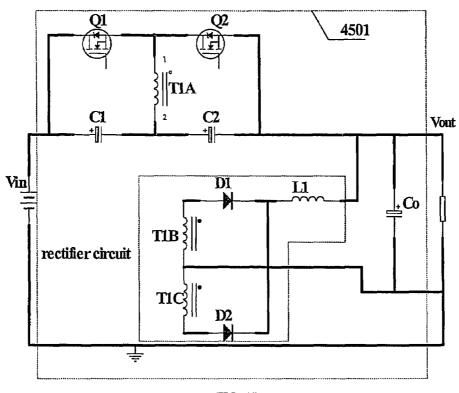

- FIG. 45 is a schematic diagram of another embodiment of 65 a non-isolated half-bridge DC converter embodiment of the converter of FIG. 3;

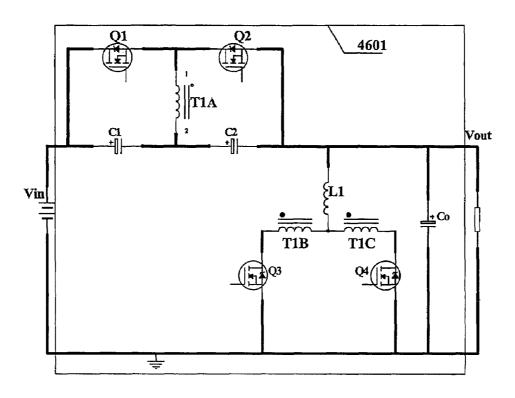

- FIG. 46 is a schematic diagram illustrating the use of a synchronous rectifiers instead of diodes in the converter of

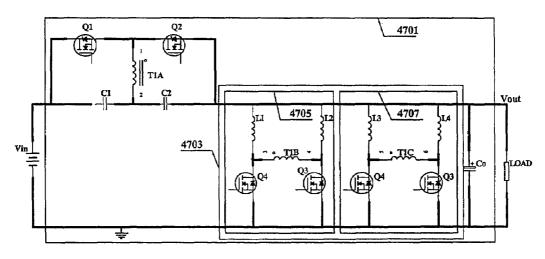

- FIG. 47 is a schematic diagram of a non-isolated halfbridge DC converter embodiment of the converter of FIG. 3 with two rectifier sections;

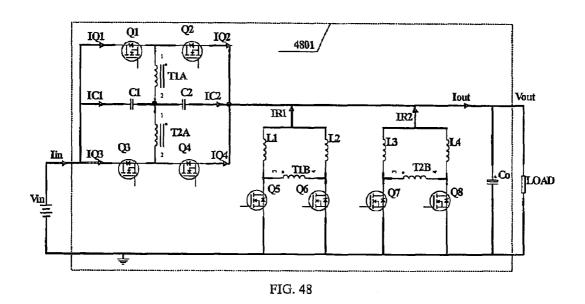

- FIG. 48 is a schematic diagram of a two-phase interleaved non-isolated half-bridge DC converter embodiment of the converter of FIG. 3;

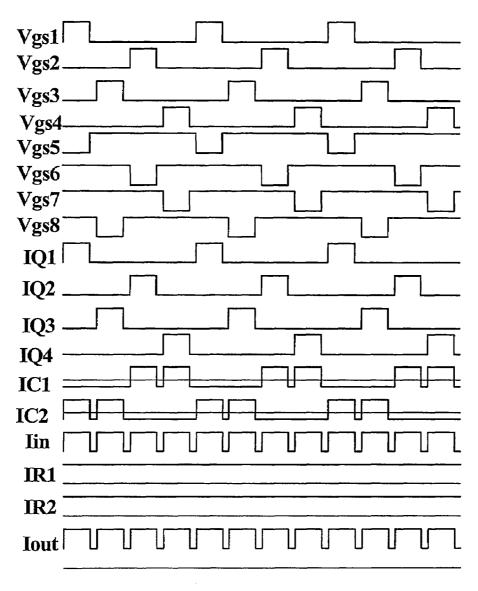

- FIG. 49 is a graphic illustration of gate drive signals other waveforms for the two-phase interleaved non-isolated halfbridge DC converter embodiment of FIG. 48 with a duty cycle of 40%;

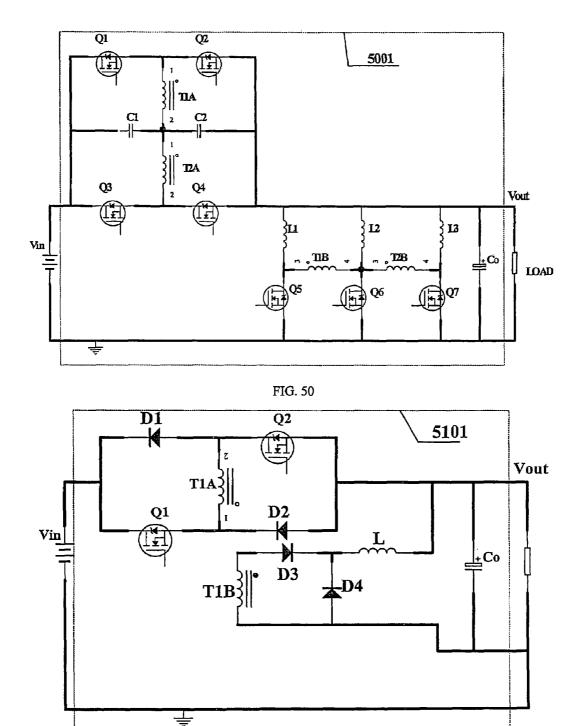

- FIG. 50 is a schematic diagram of a two-phase interleaved half-bridge DC converter embodiment of the converter of FIG. 3 with secondary shared switches;

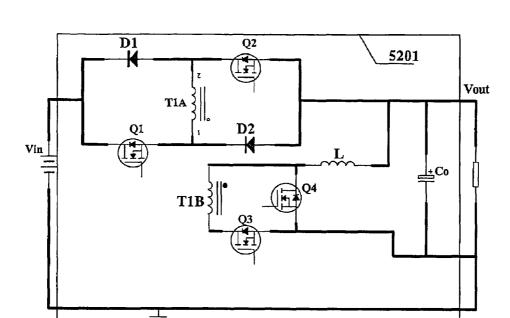

- FIG. 51 is a schematic diagram of a non-isolated forward DC converter embodiment of the converter of FIG. 3;

- FIG. 52 is a schematic diagram of the non-isolated  $^{20}$  forward DC converter embodiment shown in FIG. 51 when synchronous rectifiers are used;

- FIG. 53 is a schematic diagram of a non-isolated forward DC converter embodiment of FIG. 3 when the rectifier circuit shown in FIG. 10 is used;

- FIG. 54 is a schematic diagram of another non-isolated forward DC converter embodiment of the converter of FIG.

- FIG. 55 is a schematic diagram of the non-isolated forward DC converter embodiment shown in FIG. 54 when synchronous rectifiers are used;

- FIG. 56 is a schematic diagram of the non-isolated forward DC converter embodiment of FIG. 54 when the rectifier circuit shown in FIG. 10 is used;

- FIG. 57 is a schematic diagram of another non-isolated forward DC converter embodiment of the converter of FIG. 3 when a third winding is used to reset the transformer core;

- FIG. 58 is a schematic diagram of a two-phase interleaved non-isolated forward DC converter embodiment of the circuit shown in FIG. 51;

- FIG. 59 is a schematic diagram of a two-phase interleaved non-isolated forward DC converter embodiment of the circuit shown in FIG. 52;

- FIG. 60 is a schematic diagram of a two-phase interleaved non-isolated forward DC converter embodiment of the circuit shown in FIG. 53;

- FIG. 61 is a schematic diagram of a two-phase interleaved non-isolated forward DC converter embodiment of the circuit shown in FIG. 54

- FIG. 62 is a schematic diagram of a two-phase interleaved non-isolated forward DC converter embodiment of the circuit shown in FIG. 55;

- FIG. 63 is a schematic diagram of a two-phase interleaved non-isolated forward DC converter embodiment of the circuit shown in FIG. 56;

- FIG. 64 is a general schematic diagram of two-phase interleaved non-isolated DC converter for current sensing and current sharing;

- FIG. 65 is a schematic diagram showing one implemen-60 tation of current sensing circuit for two-phase interleaved full-bridge DC converter;

- FIG. **66** is a schematic diagram showing one implementation of current sensing circuit for two-phase interleaved half-bridge DC converter;

- FIG. 67 is a schematic diagram showing one implementation of current sensing circuit for two-phase interleaved forward DC converter;

- FIG. **68**A is a block diagram of a non-isolated DC converter in accordance with an alternate preferred embodiment of the present invention;

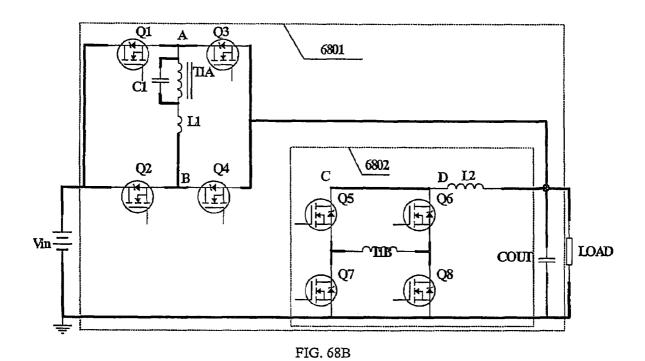

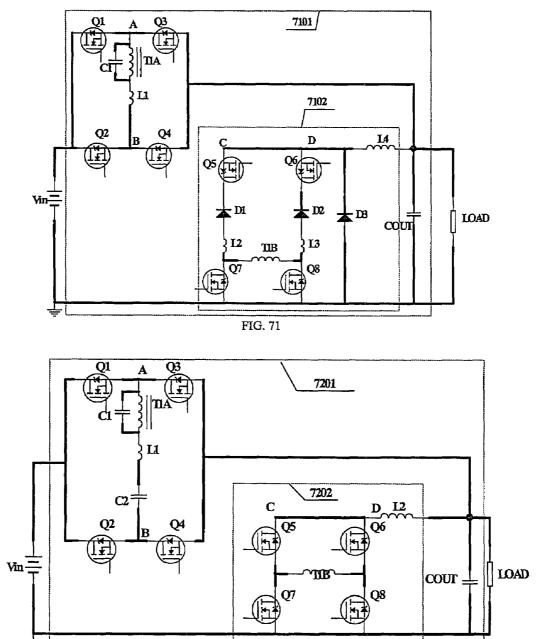

- FIG. **68**B is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the 5 converter of FIG. **68**A with full-bridge rectifier;

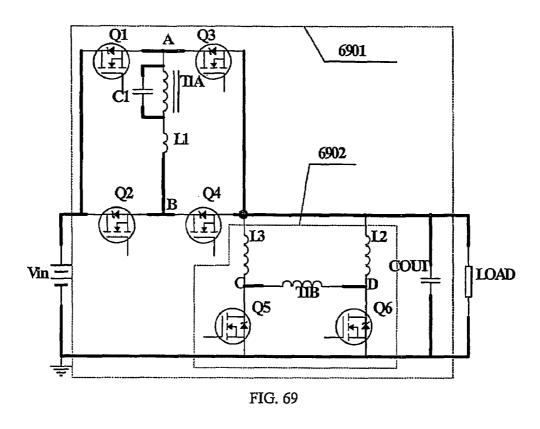

- FIG. **69** is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the converter of FIG. **68**A with current doubler rectifier;

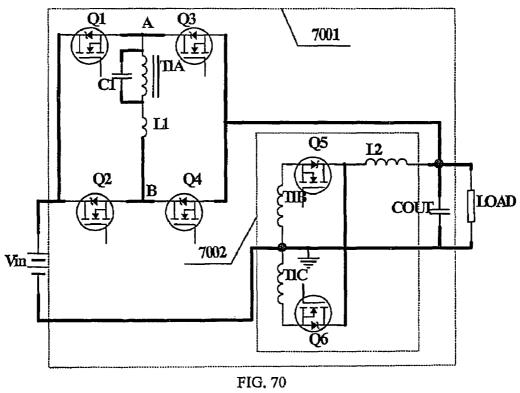

- FIG. **70** is a schematic diagram of a non-isolated parallel 10 resonant full-bridge DC-DC converter embodiment of the converter of FIG. **68**A with center tapped transformer rectifier:

- FIG. **71** is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the 15 converter of FIG. **68**A with phase control rectifier;

- FIG. 72 is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the converter of FIG. 68A with LCC resonant tank and full-bridge rectifier;

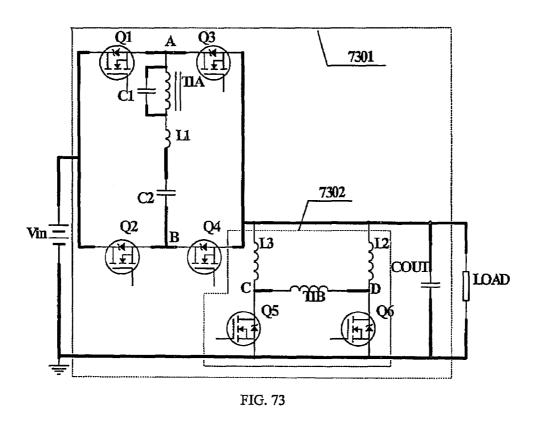

- FIG. 73 is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the converter of FIG. 68A with LCC resonant tank and current doubler rectifier:

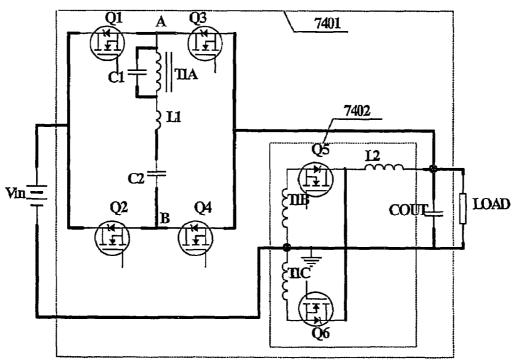

- FIG. **74** is a schematic diagram of a non-isolated parallel 25 resonant full-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCC resonant tank and center tapped transformer rectifier;

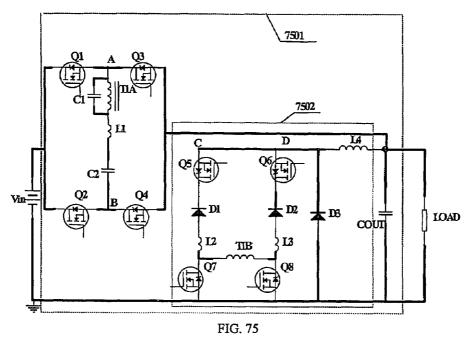

- FIG. **75** is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the 30 converter of FIG. **68**A with LCC resonant tank and phase control rectifier;

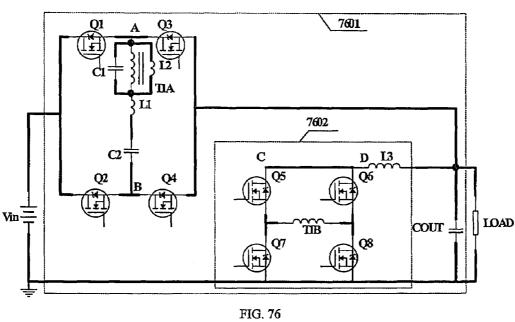

- FIG. **76** is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCLC resonant tank and full- 35 bridge rectifier:

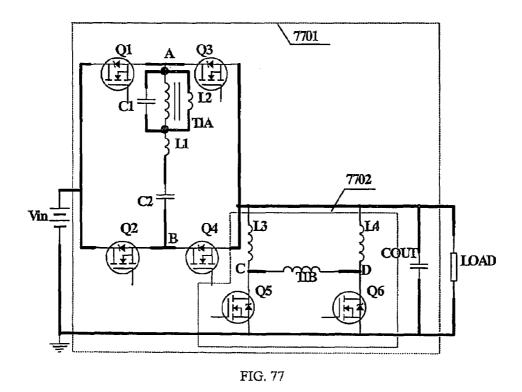

- FIG. 77 is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the converter of FIG. 68A with LCLC resonant tank and current doubler rectifier;

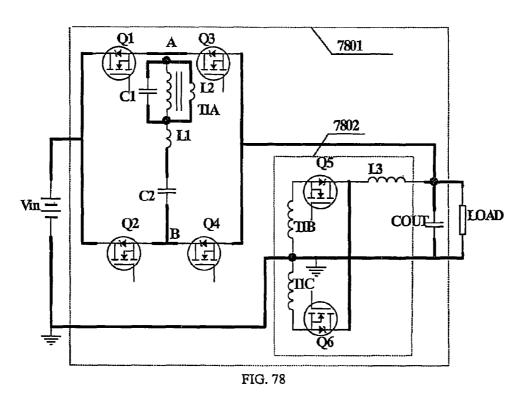

- FIG. **78** is a schematic diagram of a non-isolated parallel resonant full-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCLC resonant tank and center tapped transformer rectifier;

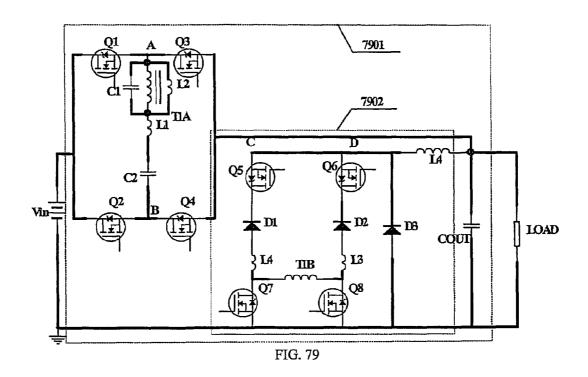

- FIG. **79** is a schematic diagram of a non-isolated parallel 45 resonant full-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCLC resonant tank and phase control rectifier;

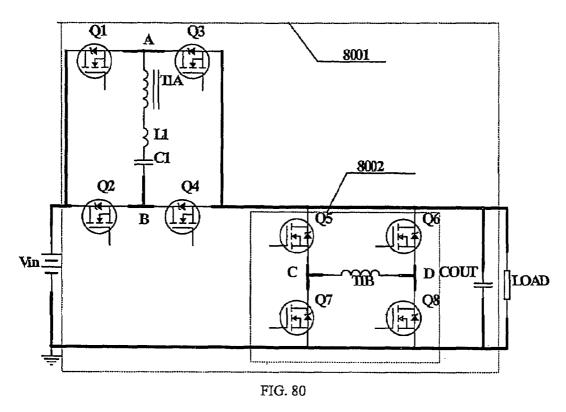

- FIG. **80** is a schematic diagram of a non-isolated series resonant full-bridge DC-DC converter embodiment of the 50 converter of FIG. **68**A with full-bridge rectifier;

- FIG. **81** is a schematic diagram of a full-bridge series resonant converter embodiment of the converter of FIG. **68**A with center tapped transformer rectifier;

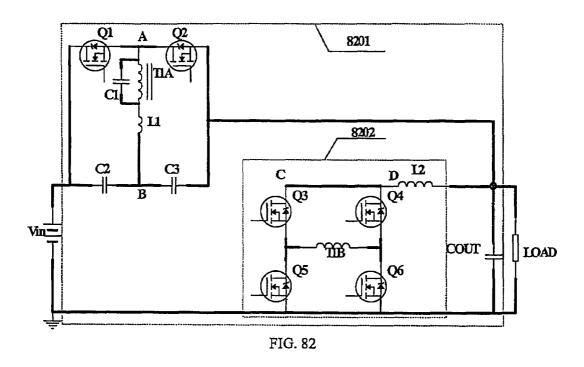

- FIG. **82** is a schematic diagram of a non-isolated parallel 55 resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with full-bridge rectifier;

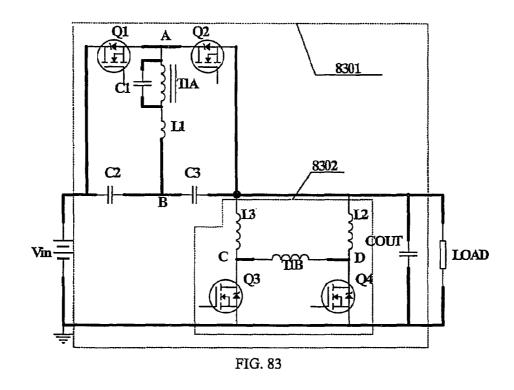

- FIG. **83** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC Converter embodiment of the converter of FIG. **68**A with current doubler rectifier;

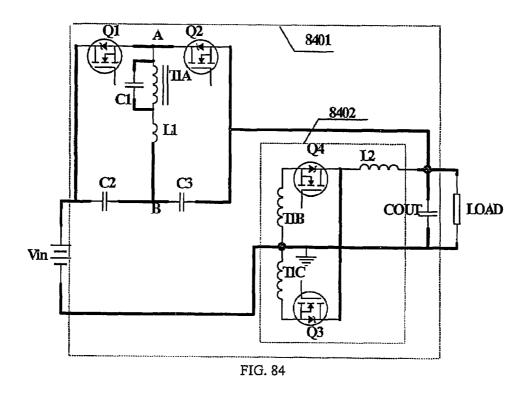

- FIG. **84** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with center tapped transformer rectifier;

- FIG. **85** is a schematic diagram of a non-isolated parallel 65 resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with phase control rectifier;

12

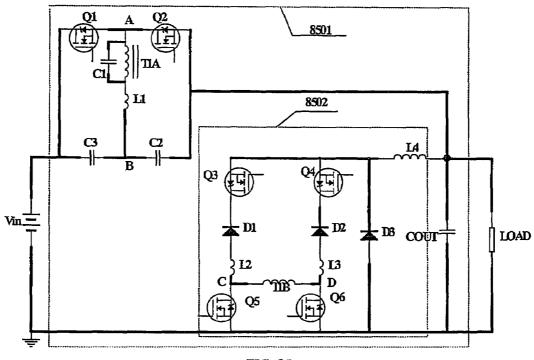

- FIG. **86** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-D Converter embodiment of the converter of FIG. **68**A with LCC resonant tank and full-bridge rectifier;

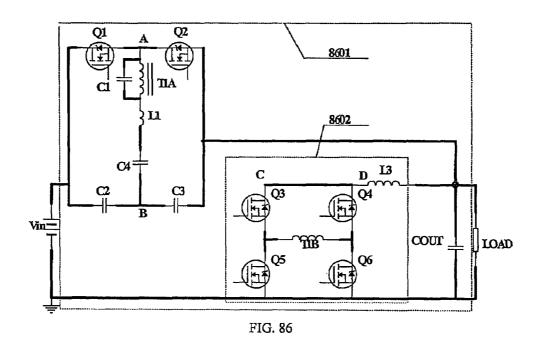

- FIG. **87** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCC resonant tank and current doubler rectifier;

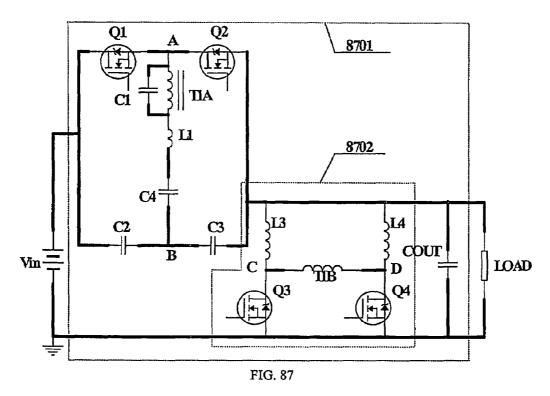

- FIG. **88** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCC resonant tank and center tapped transformer rectifier;

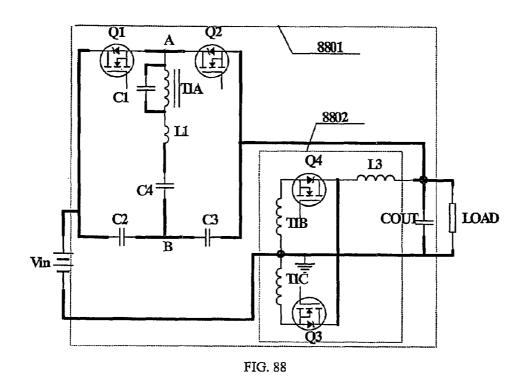

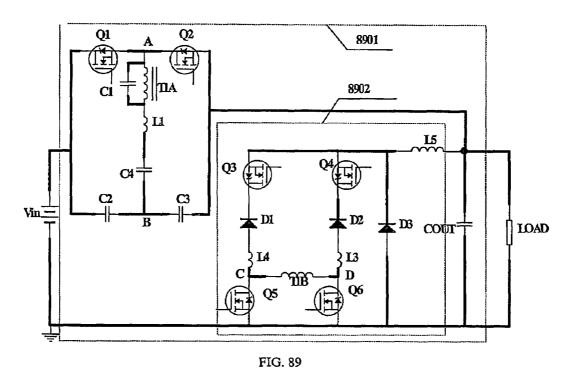

- FIG. **89** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCC resonant tank and phase control rectifier;

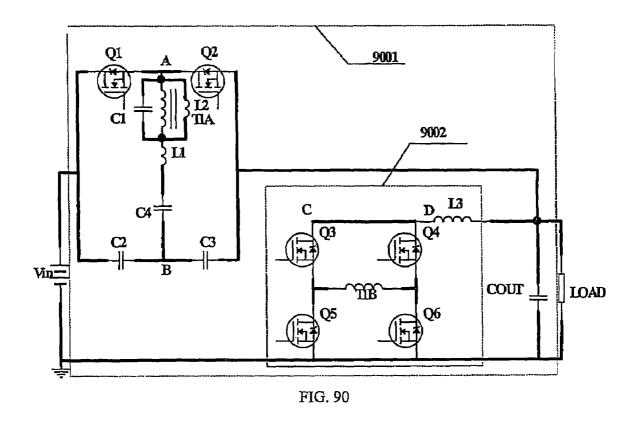

- FIG. **90** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCLC resonant tank and full-bridge rectifier;

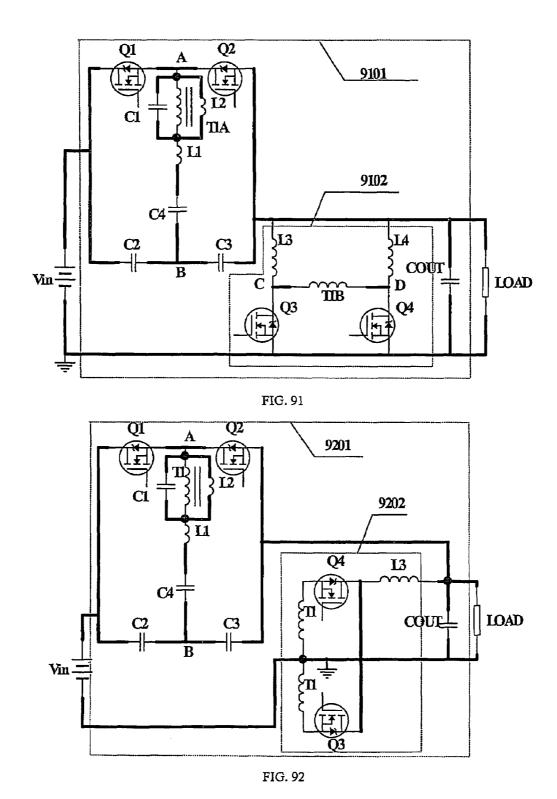

- FIG. **91** is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with LCLC resonant tank and current doubler rectifier:

- FIG. 92 is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. 68A with LCLC resonant tank and center tapped transformer rectifier;

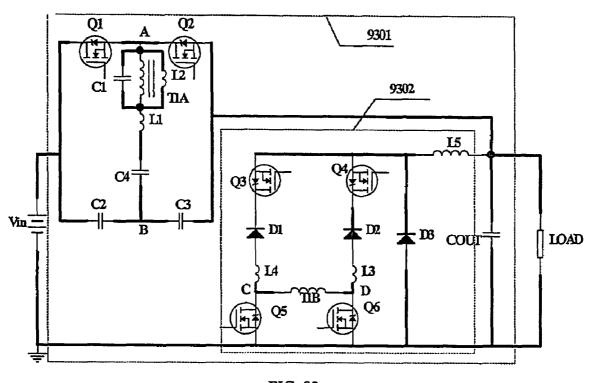

- FIG. 93 is a schematic diagram of a non-isolated parallel resonant half-bridge DC-DC converter embodiment of the converter of FIG. 68A with LCLC resonant tank and phase control rectifier;

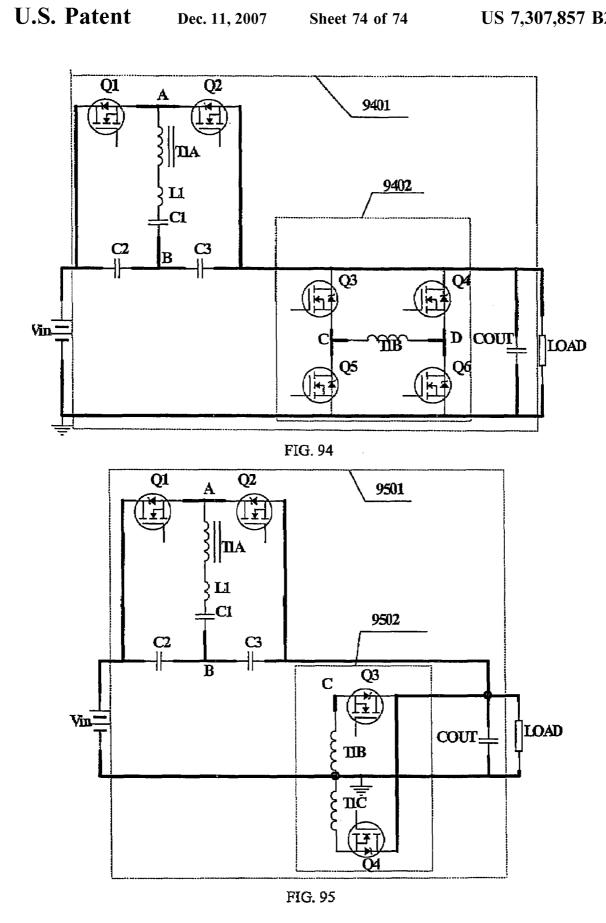

- FIG. **94** is a schematic diagram of a non-isolated series resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with full-bridge rectifier; and

- FIG. **95** is a schematic diagram of a non-isolated series resonant half-bridge DC-DC converter embodiment of the converter of FIG. **68**A with center tapped transformer rectifier

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

Referring to FIG. 3, a non-isolated DC converter 301 (outlined in dashed lines) consists of three blocks: high side circuit 305, rectifier circuit 307 and output filter capacitor Co. The high side circuit 305 connects directly between positive point  $V_{in+}$  of the input voltage  $V_{in}$  and the positive point  $V_{out+}$  of the output  $V_{out-}$  The high side circuit 305 is therefore not isolated from the rectifier circuit 307 and, thus, the converter is "non-isolated".

As will be discussed, the high side circuit 305 includes one or more transformer primary winding(s) and an auxiliary section that will operate the transformer(s) properly. This auxiliary section may consist of switches (such as MOSFET, BJT ("bipolar junction transistor"), etc). This auxiliary section may also consist of a combination of switches and capacitors. The function of this auxiliary section is to make the transformer operate properly. The term "operate properly" means that the transformer will not saturate and the power can be transferred from each primary winding to its secondary winding(s) efficiently. Various examples of auxiliary sections, such as full-bridge, half-bridge, and forward will be described herein.

The high side circuit 305 serves two functions. One is that it converts the electrical energy into magnetic energy

through the transformer primary winding(s). The other function is to transfer energy directly to the output voltage  $V_{out}$ .

The converter **301** can be used to meet the stringent power requirement of the next generation CPU. The circuit topologies described herein are able to achieve high efficiency, fast 5 dynamic response and provide high current to the CPU.

Also to be described are methods of operating the non-isolated DC converter 301. Using these methods, the non-isolated DC converter will operate with a large duty cycle and at the same time, have a large input voltage to output 10 voltage conversion ratio.

Referring to FIG. 4, one embodiment 401 of the high side circuit 305 consists of one primary winding of transformer T1A and four MOSFETs Q1, Q2, Q3, Q4. The left point A of the high side circuit 401 is connected to Vin and the right 15 point B of the high side circuit 401 is connected to Vout.

Gate drive signals of Q1, Q2, Q3, and Q4 should be arranged so that transformer T1A can operate properly. Referring to FIG. 5, one example of such as arrangement is shown as Vgs1, Vgs2, Vgs3 and Vgs4. The gate signals 20 Vgs1 and Vgs4 for Q1 and Q4 are the same and gate signals Vgs2 and Vgs3 for Q2 and Q3 are the same. In the figure, a high voltage level means the MOSFET is turned on and a low voltage level means the MOSFET is turned off.

Referring to FIG. 6, another embodiment 601 of the high 25 side circuit 305 is shown. The high side circuit 601 consists of one transformer primary winding T1A, two MOSFETs Q1, Q2 and two capacitors C1, C2. The left point A of the high side circuit 601 is connected to Vin and the right point B of the high side circuit is connected to Vout.

The value of C1 and C2 should be large enough so that the voltage across C1 and C2 does not change significantly during normal operation of the circuit 601. In other words, the voltage across C1 and C2 is a DC voltage with small voltage ripple. The gate drive of Q1 and Q2 should be 35 arranged so that transformer T1A can operate properly. Referring to FIG. 7, one example of such as arrangement is shown as Vgs1 and Vgs2.

Referring to FIG. **8**, another embodiment **801** of the high side circuit **305** is shown. This embodiment **801** consists of 40 one transformer primary winding T1A, two MOSFETs Q1,Q2 and two diodes D1, D2. The left side A of the high side circuit **801** is connected to the input voltage Vin. The right side B of the high side circuit **801** is connected to the output voltage Vout.

Q1 and Q2 are turned on at same time. When Q1 and Q2 are off, magnetizing current flows through D1 and D2 from point B to point A and thus resets the core of transformer T1.

Referring to FIG. 9, another embodiment 901 of the high side circuit 305 is illustrated using one transformer primary 50 winding T1A, two MOSFETS Q1,Q2 and one capacitor C1. Point A is connected to the input voltage Vin and point B is connected to the output voltage Vout.

It is noted that MOSFET Q1 carries input current. MOSFET Q2 carries only the magnetizing current. When Q1 is 55 on, Q2 is off. When Q1 is off, Q2 is on. The voltage developed across C1 is used to reset the core of transformer T1.

It is noted that there are other embodiments of the high side circuit **305** as will be evident to one skilled in the art 60 using this description. Not all of them have been described, nor will they be. Some additional examples will be given

Returning to FIG. 3, the rectifier circuit 307 is connected in parallel with the output voltage Vout and in parallel with 65 the output capacitor Co. It includes one or more transformer secondary winding(s). It includes diodes that will convert

14

the bi-directional voltage from the transformer secondary winding into a pulsating, one-direction voltage. In addition, it consists of one or more inductors that will convert the pulsating, one-direction voltage through the secondary winding(s) into a DC voltage.

It is noted that the diodes can be replaced by MOSFETs in order to reduce the power loss.

The function of the rectifier circuit 307 is to convert the AC voltage from the transformer secondary winding(s) into a DC voltage Vout. It also provides a portion of the total load current.

Referring to FIG. 10, one embodiment 1001 of the rectifier circuit 307 is shown. In this case, the rectifier circuit 1001 includes one transformer secondary winding T, two MOSFETs Q1,Q2 and two inductors L1,L2. The top point C is connected to the positive point Vout+ of output voltage Vout. The bottom point D is connected to negative point Vout- of the output voltage Vout. In this embodiment, MOSFETs Q1 and Q2 are used as synchronous rectifiers to reduce power loss. The waveform of the gate drive signals Vgs1, Vgs2 for Q1 and Q2 will depend on the connection of the high side circuit 305. The objective of Q1 and Q2 is to convert bi-directional AC voltage that appears at the transformer secondary winding T into one-direction pulsating voltage.

Referring to FIG. 11, another embodiment 1101 of the rectifier circuit 307 is shown. In this case, the rectifier circuit 1101 consists of one transformer secondary winding T1B, two MOSFETs Q1,Q2 and one inductor L. The top point C is connected to the positive point Vout+ of output voltage Vout. The bottom point D is connected to negative point Vout- of the output voltage Vout. MOSFETs Q1,Q2 are used as synchronous rectifiers to reduce the power loss. The waveform of the gate drive signal Vgs1, Vgs2 for Q1 and Q2 will depend on the connection of the high side circuit 305. The objective of Q1 and Q2 is to convert the bi-directional AC voltage that appears at the transformer secondary winding T1B into one-direction pulsating voltage.

Referring to FIG. 12, when the MOSFETs Q1, Q2 in FIG. 11 are replaced by diodes D1, D2, another embodiment 1201 of the rectifier circuit 307 is obtained. In this figure, the diodes D1, D2 are used to convert the bi-directional voltage across the transformer secondary winding T1B into one-direction pulsating voltage. Inductor L is used to filter the pulsating voltage into DC voltage Vout.

Some rectifier circuits 307 consist of two transformer secondary windings. Referring to FIG. 13, a rectifier circuit 1301 with two transformer secondary windings T1B, T1C is shown. It uses two diodes D1, D2 as rectifier switches. It uses only one inductor L.

Referring to FIG. 14, another rectifier circuit 1401 with two secondary windings T1B, T1C and synchronous rectifiers Q1, Q2 is shown. It requires one inductor L.

As will be evident to those skilled in the art using this description, there are other embodiments of the rectifier circuit 307 that have not been described herein.

Referring again to FIG. 3, the output capacitor Co is connected in parallel with the load circuit LOAD. It is also connected in parallel with the rectifier circuit 307. The function of the output capacitor Co is to absorb the pulsating current that comes from the high side circuit 305. The value of the output capacitor Co should be large enough to provide a DC voltage across the load.

If the capacitor Co is not used, the output voltage Vout may have significant ripple voltage such that the load LOAD may not operate properly.

It should be noted that the high side circuits described above only show the basic operation and requirement of the high side circuit **305** as shown in FIG. **3**. In actual implementation, some modification of the above high side circuits can be added to further improve the operation of the high side circuits. For example, leakage inductance of the transformer can be intentionally designed larger to make the MOSFET switches operate at more favourable conditions. A snubber circuit can be added to reduce the power dissipated in the MOSFETs, diode, or transformer. Some other auxiliary circuit can be added around the MOSFETs to make the operation of these MOSFETs more favourable, such as reducing the switching loss.

It should also be noted that the rectifier circuits described above only show the basic operation and requirement of the rectifier circuit 307 as shown in FIG. 3. In actual implementation, some modification of the above rectifier circuits can be added to further improve operation of the rectifier circuits. For example, the gate drive signals for the synchronous rectifier switches used in the rectifier circuit 307 can be 20 derived from the transformer secondary winding to simplify the gate drive circuit. Other gate drive timing circuits can be added to further improve the operation of the synchronous rectifier. A snubber circuit may also be added across the synchronous rectifiers or diodes to reduce the power dissipation.

In addition, it should be noted that only one capacitor Co is used as the output filter to smooth output voltage. In actual implementation, other additional filters can be added after Co. For example, a pi filter can be used to further reduce the 30 output voltage ripple. Similarly, no input filter is shown in the circuit diagram of FIG. 3. In actual implementation, at least a capacitor is needed to provide the input ripple current so that the DC source does not need to provide the ripple current. This is usually the preferred implementation. Additional EMI filters can be used to reduce the noise injected into input voltage source.

In converter 301, as shown in FIG. 3, the high side circuit 305 is connected between the positive point of the input voltage (Vin+) and the positive point of the output voltage 40 (Vout+). It should be noted that the converter 301 will also operate properly when the high side circuit is connected between the negative point of the input voltage (Vin-) and the negative point of the output voltage (Vout-). In this implementation, different components might be used for the 45 high side circuit. The connection of the components might also be changed to make the high side circuit operate properly. Based on the fact that in actual implementation, it is preferred to put the high side circuit between the positive points of Vin and Vout, the following description assumes 50 that connection. Nevertheless, the circuit 301 will operate when the high side circuit 305 is connected between the negative points of Vin and Vout.

Thus, the voltage inputs to the converters could simply be a first voltage and a second voltage, rather than always being positive and negative DC voltages (or "potentials") with the positive voltage always being the input voltage to the high side circuit. Similarly, the output voltage of the converter could be first and second DC voltages, rather than requiring the converter output that receives current from the high side 60 circuit to be a positive voltage when compared to the other converter output. In any case the output converter DC voltage between the first voltage and the second voltage has the same polarity as a DC voltage input between the first voltage and the second voltage.

Accordingly, the term "high side circuit" is used herein although the high side circuit may be in the low side of the

16

converter. The "high side circuit" could alternatively be referred to as a "primary side" or "primary side circuit". Similarly, "rectifier circuit" could alternatively be referred to as a "secondary side" or "secondary side circuit".

All of the above variations and any other variations to converters employing the principles described herein are included within the scope of those principles and the invention as later claimed.

Several non-isolated full-bridge DC converters will be described. In these DC converters, the high side circuit 301 includes four MOSFETs as switches and one transformer primary winding, as shown in FIG. 3. An embodiment of a rectifier circuit 307 using multiple rectifier sections (duplicated rectifier circuits) connected in parallel will also be discussed.

Referring to FIG. 15, a non-isolated full-bridge DC converter 1501 is shown.

The full-bridge converter **1501** topology includes six MOSFETs Q1-Q6, one transformer T1, with one primary winding T1A and one secondary side winding T1B, two inductors L1, L2 and one output capacitor Co. The operation of the circuit **1501** will be discussed later below.

Q1, Q2, Q3 and Q4 are primary switches. They can be implemented, for example, by IRL7467 from International Rectifier. This is true for all the primary switches described herein. The drains of Q1 and Q3 are connected together and then connected to the positive terminal of the input voltage Vin+. The source of Q1 and the drain of Q2 are connected together. The source of Q3 and the drain of Q4 are connected together. The source of Q2 and Q4 are connected together and then connected to the output voltage terminal Vout+.

Q5 and Q6 are synchronous rectifier switches. They can be replaced by diodes. Q5 and Q6 can be implemented by, for example, IRLR8103 from International Rectifier. This is true for each of the secondary MOSFETs described herein. The sources of Q5 and Q6 are connected together and then are connected to ground point (or negative terminal of input voltage, which is the same point as negative terminal of output voltage Vout-). The drain of Q5 is connected with one terminal of inductor L1. The other terminal of L1 is connected to the positive point of output voltage Vout+. The drain of Q6 is connected with one terminal of L2. The other terminal of L2 is connected to the positive terminal of the output voltage Vout+.

The primary winding T1A is connected between the drain of Q2 and drain of Q4. The secondary winding T1B of transformer T1 is connected between drain of Q5 and drain of Q6.

For VRM applications, Q1, Q2, Q3 and Q4 are almost exclusively implemented using MOSFETs. However, other switches, such as power transistors, IGBTs ("insulated gate bipolar transistors"), GTOs ("gate turn off" thyristors), etc, can also be used. This is again true for all the primary switches described herein.

Q5 and Q6 are each operating in synchronous rectifier mode, which means that under normal operating condition, the current will flow from the source terminal to drain terminal. It is noted that Q5 and Q6 can be replaced by diodes. However, the efficiency will be reduced for VRM application because the loss will be much higher for diodes.

Transformer T1 can be implemented, for example, using a conventional wire wound transformer. It can also be implemented, for example, using a planar transformer. It is noted that for VRM application, the planar transformer will be preferred because it can reduce the power loss and reduce the cost. This is true for all the transformers described herein.

The inductors L1, L2 can be implemented, for example, using off the shelf wire wound inductor. It can also be implemented, for example, using planar inductor. This is true for all the inductors described herein.

For a typical application of a converter **301**, the input 5 voltage is 12V (which can be changed from 10.8V to 13.2V) and the output voltage is 1.5V (which can be changed from 0.8V to 1.6V). The turns ratio of the transformer, defined as the ratio of secondary turn, Ns, and primary turn, Np, N=Ns/Np, is selected as 0.667 (or Ns=2, Np=3). Then the 10 required duty cycle for Q1, defined as the ratio of on time of Q1, TonQ1, over the half switching period of Q1, 0.5\*Ts, D=TonQ1/(0.5\*Ts) is about 0.5, when the loss of the converter **301** is considered. When the duty cycle is around 0.5, the performance of the converter is optimized.

The non-isolated full-bridge DC converter **1501**, as shown in FIG. **15**, has the advantage of higher conversion efficiency. This is because the primary and secondary sides (high side circuit and rectifier circuit) are not isolated;, i.e., the primary and secondary sides are coupled directly. This will increase the efficiency, or equivalently, reduce the power loss during conversion. This will significantly improve the life of the converter **1501**, as the junction temperature of semiconductors is reduced. In addition, this will make the converter size smaller. It can also simplify the 25 mechanical design of a computer motherboard, which can reduce the cost.

As primary current goes directly to the load, this can reduce the current stress of the secondary synchronous rectifiers Q5, Q6. The current ripple in the two output inductors L1, L2 will be cancelled by each other, which reduces the output current ripple significantly. Smaller current ripple means it is possible to select a smaller output capacitor Co. A smaller output capacitor Co and, possibly, smaller inductor L can provide the converter 1501 with <sup>35</sup> faster dynamic response.

The operation of the full-bridge converter 1501 can more easily be understood if it is assumed that all the components are ideal. In this analysis, the gate drive signals Vgs1-Vgs6 for Q1, Q2, Q3, Q4, Q5, and Q6 shown in FIG. 19 are used. There are four operating periods. The operation can be explained by using the equivalent circuits shown in FIG. 16, FIG. 17, and FIG. 18, and waveforms shown in FIG. 19. It should be noted that other gate drive schemes can also be used to drive Q1, Q2, Q3, Q4, Q5, and Q6. One such example is the phase shifted PWM gate drive scheme, as shown in FIG. 20.

Referring to FIG. 19, the main waveforms for the full-bridge converter 1501 are:

- 1. Vgs1 to Vgs6 are the gate signals of the 6 switches.

- 2. Iin is the input current. IL1 and IL2 are the current in L1 and I.2.

- 3. IQ5 and IQ6 are the current in switches Q5 and Q6.

- 4. VL1 and VL2 are the voltage across L1 and L2.

Referring to FIG. 19, in Interval 1: From time t0 to t1, Q1, Q4 and Q6 are on, resulting in the equivalent circuit 1601 shown in FIG. 16. The input current Iin flows through Q1 and Q4 to the load side. The inductor current IL1 also flows into the load side. Current in inductor L1 rises and current in L2 is falling.

Again referring to FIG. 19, at Interval 2: from time t1 to t2, Q1 and Q4 are turned off and Q5 is turned on, resulting in the equivalent circuit of FIG. 17. Therefore, Q1, Q2, Q3 and Q4 are off and Q5 and Q6 are on. At this time, the input 65 current is zero and the current in L1 and L2 is falling. The energy stored in L1 and L2 is released to the load. The

18

transformer secondary winding is shorted. The equivalent circuit 1701 is shown in FIG. 17.

Again referring to FIG. 19, at Interval 3: from time t2 to time t3, Q2 and Q3 are turned on and Q6 is turned off. The on devices for this interval are Q2, Q3 and Q5. The input current flows through Q2 and Q3 to the load, inductor current in L2 is rising and the current in L1 is falling. The equivalent circuit 1801 is shown in FIG. 18.

Again referring to FIG. 19, at Interval 4: from time t3 to t4, Q2 and Q3 are turned off and Q6 is turned on again. Q1, Q2, Q3 and Q4 are off and Q5, Q6 are on. This stage is the same as interval 2. At this time, the input current Iin is zero, and current IL1 and IL2 in L1 and L2 are falling. The transformer secondary winding T1B is shorted. The equivalent circuit 1701 is shown in FIG. 17.

In the above analysis, the regular PWM gate drive scheme as shown in FIG. 19 is used. A phase-shift PWM gate drive scheme is shown in FIG. 20.

The main difference between the regular PWM control and phase-shift PWM control is that the latter introduces one operating interval when both Q1 and Q3 are on. During this period, the transformer primary winding T1A is shorted. One advantage of the phase-shifted PWM gate drive scheme is that zero voltage switching ("ZVS") for Q1, Q2, Q3 and Q4 can be achieved by the leakage inductance of the transformer T1 and by the load current. This can reduce the switching loss of Q1, Q2, Q3 and Q4. In addition, it reduces the core loss of the transformer Ti by reducing the peak to peak flux density.

Based on the above analysis, some equations for the non-isolated full-bridge DC converter **1501** under ideal conditions will be discussed.

Relationship of output voltage Vout and input voltage Vin is shown in the following equation:

$$Vout = Vin*N*D/(2+N*D), N=Ns/Np$$

(1)

In the above equation, D is the total duty cycle and defined by D=2\*Ton/Ts, where Ton is the on time of Q1 and Ts is the switching period of Q1. Ns is the turns for transformer secondary winding T1B and Np is the turns for transformer primary winding T1A. N is the turns ratio. This equation can be used to determine the turns ratio for a given application.

The relationship between the input current Iin and output current Io is shown in the following equation:

$$I_{\text{in\_avg}} = I_{\text{o\_avg}} \frac{ND}{ND + 2}$$

(2)

The above equation can be used to determine the input current requirement. It can also be used to calculate the rms (root mean square) current of MOSFETs Q1, Q2, Q3, and Q4.

The voltage stress of primary MOSFETs Q1, Q2, Q3, and Q4 is given by the following equation.

$$V_{PMOSFET} = V_{in} - V_{out}$$

(3)

This equation is used to select MOSFETs with sufficient voltage rating. For example, for a 12V input, a MOSFET with 15V voltage rating can be used.

The rms current in primary MOSFETs Q1, Q2, Q3, and Q4 is given by the following equation:

$$I_{\text{PMOSFET\_RMS}} = \frac{I_{\text{in}}}{\sqrt{D}} \frac{\sqrt{2}}{2} \tag{4}$$

The above equation can be used to select MOSFETs with proper current rating. It can also be used to calculate the conduction loss of the MOSFETs.

The current ripple in the output inductors L1, L2 is given  $_{10}$  in the following equation.

$$\Delta I_L = \frac{V_o}{L} (1 - D/2)Ts \tag{7}$$

In the above equation, L is the inductor value. This equation is used to calculate the peak inductor current, which is required to calculate the switching loss, and design the inductors L1, L2.

The average current in the output inductors L1, L2 is given in the following equation:

$$I_{Lavg} = \frac{(I_o - I_{inovg})}{2} = \frac{I_o}{2} \left(\frac{2}{ND + 2}\right)$$

(8)

The above equation is used to calculate the rms current for Q5 and Q6, as well as to design the inductors L1, L2.

The rms current through each synchronous rectifier Q5, Q6 is given by the following equation:

$$I_{\text{syn\_RMS}} = \sqrt{(1 - D)I_{Lavg}^2 + \frac{D}{2}(I_{L1avg} + I_{L2avg})^2}$$

(9)

The above equation can be used to select the synchronous rectifier MOSFETs Q5 and Q6.

The above equations can be used to design the full-bridge converter **1501**.

The above section describes in detail the operation and some advantages of the non-isolated full-bridge DC converter 1501 under the assumption that all the components are deal. It should be noted that under actual condition, the operation will be a little bit different from the above analysis as will be evident to those skilled in the art using this description.

It is also noted that by using the phase-shift PWM gate 50 drive scheme of FIG. 20 for Q1, Q2, Q3 and Q4, zero voltage switching for the primary MOSFETs Q1, Q2, Q3, Q4 can be achieved. This is beneficial in reducing the switching loss and/or increasing the switching frequency.

The previous section discusses in detail the basic non-isolated full-bridge DC converter **1501**. It should be noted that when different rectifier circuits **307** are used, other types of non-isolated full-bridge DC converter can be derived. In this section, two alternative embodiments of a non-isolated full-bridge DC converter will be described. Their operation is similar to the original embodiment **1501** as shown in FIG. **15**. As will be evident to those skilled in the art, other embodiments can also be derived using similar methods.

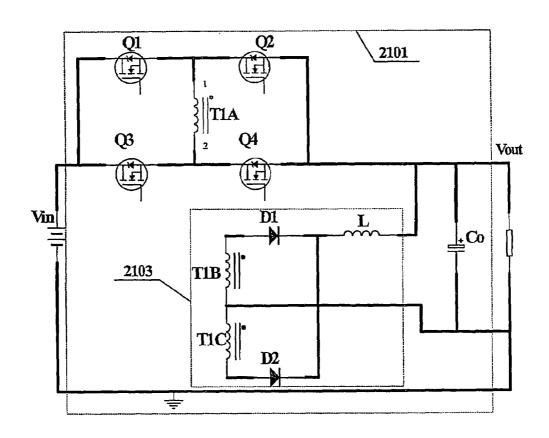

Referring to FIG. 21, another embodiment 2101 of a non-isolated full-bridge converter is shown. In this embodiment, the rectifier circuit includes two secondary windings of the transformer. Diode D1 and D2 are used to convert the

bi-directional voltage across the secondary windings of the transformer T1 into one-direction pulsating voltage. Only one inductor L is used.

Referring to FIG. 22, when the diodes D1, D2 in the circuit 1501 shown in FIG. 15 are replaced by synchronous rectifiers Q5, Q6 in order to reduce the power loss in low output voltage applications, the circuit 2201 is obtained. The position of Q5, Q6 is interchanged with the secondary winding T1B, T1C in order to simplify the requirement for the gate drive of Q5 and Q6.

In order to increase the current carrying capability or to reduce power loss in a rectifier circuit, two or more rectifier sections can be connected in parallel.

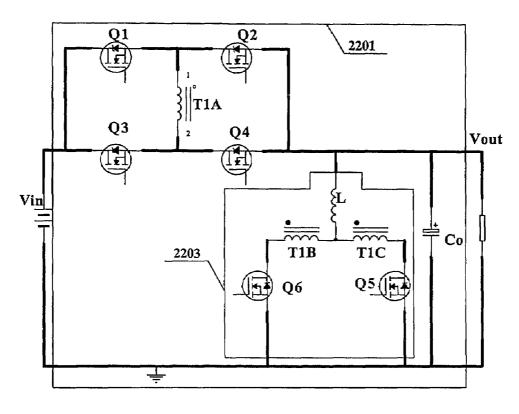

Referring to FIG. 23, one such circuit 2301, which is based on circuit 1501 in FIG. 15, is derived by using two rectifier sections 2303, 2305 (each section forming its own rectifier circuit). The two rectifier sections 2303, 2305 are connected in parallel. One rectifier section 2303 consists of Q5, Q6, L1, L2 and one secondary winding T1C. The other rectifier section 2305 consists of Q7, Q8, L3, L4 and one transformer secondary winding T1B. Transformer T1 has one primary winding T1A (same as in FIG. 15), and has two secondary windings T1B, T1C. These three windings T1A, T1B, T1C are coupled together through magnetic core of transformer T1.

Using this method the output load current is shared in the two secondary windings T1B, T1C. As we know the conduction losses are I<sup>2</sup>R, if the resistance is the same, and the current becomes half, the conduction losses will reduce four times. This is more effective than using two MOSFETs in parallel to reduce conduction losses when parasitic parameters are considered. In other words, two secondary windings T1B, T1C arrangement will ensure better current sharing in rectifier circuit 2301.

The major advantage of this arrangement is the reduction of the conduction loss for inductors L1-L4 and synchronous rectifiers Q5, Q6, Q7, Q8. When the transformer T1 is implemented by planar transformer, the cost of adding another winding is zero. The gate drive of Q7 is the same as that of Q5 and the gate drive of Q8 is same as that of Q6. When the same MOSFETs are used, the conduction loss for the rectifier circuit can be cut by half. That can increase the efficiency by about 3%.

In cost-sensitive applications, lower cost MOSFETs (which normally have higher on resistance) can be used, and the total conduction loss will be similar to that of FIG. 15, while the cost of four lower cost MOSFETs may well be lower than the cost of two premium MOSFETs.

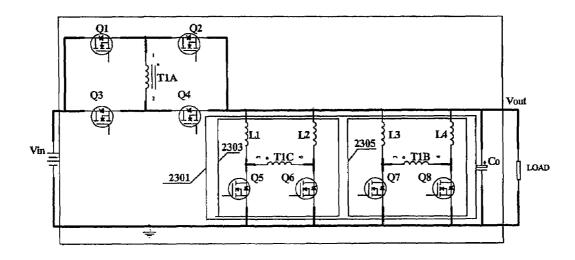

Referring to FIG. 24, another rectifier circuit embodiment 2401 including two rectifier sections 2403, 2405 is shown. In this figure, the two rectifier sections 2403, 2405 are each the same as the rectifier circuit used in FIG. 21, and they are connected in parallel. Rectifier section 2403 consists of secondary windings T1B, T1C, diodes D1 and D2, and inductor L1. Rectifier section 2405 consists of secondary windings T1D, T1E, diodes D3 and D4, and inductor L2. It is noted that all the five transformer windings, T1A, T1B, T1C, T1D and T1E, are coupled to the same magnetic core of transformer T1.

Referring to FIG. 25A, another rectifier circuit embodiment 2501 including two rectifier sections 2503, 2505 is shown. In this figure, the two rectifier sections 2503, 2505 are each the same as the rectifier circuit used in FIG. 22, and they are connected in parallel. Rectifier section 2503 consists of secondary windings T1B, T1C, MOSFETs Q5 and Q6, and inductor L1. Rectifier section 2505 consists of secondary windings T1D, T1E, MOSFETs Q7 and Q8, and

inductor L2. It is noted that all the five transformer windings, T1A, T1B, T1C, T1D and T1E, are coupled to same magnetic core of transformer T1.

It is noted that in the above discussion of FIGS. 23-25A, the number of rectifier circuits is limited to two. In actual 5 implementation, three or more rectifier sections can also be used to share the load current in order to reduce the conduction loss in the rectifier circuit.

It should be noted that in actual implementation, adding more secondary windings does not necessarily increase the 10 transformer cost when a planar magnetic structure is used; however, every time a secondary winding is added, more inductors are also needed.

In order to increase the current carrying capability, two or more identical DC converters can be connected in parallel 15 with respective inputs and outputs connected together. Interleaving is a technology that controls the turn on instant of the switches in different DC converters so that the input current ripple and output current ripple can be significantly reduced. For example, the turn on instant of one MOSFET in the 20 second converter is delayed with respect to the same MOS-FET in the first converter so that the input currents of these two converters are 180 degrees out of phase. This will result in significant reduction of the input current ripple and, therefore, reduction of the size of the input filter. By inter- 25 leaving, the output current ripple of each converter is also 180 degrees out of phase. This will also result in significant reduction of the output current ripple and, therefore, the size of the output filter. It should be noted that a smaller input filter and output filter is very beneficial in improving the 30 transient response of the converter.

One extension of the circuit 301 shown in FIG. 3 is the two-phase interleaved circuit 25A01, as shown in FIG. 25B. Referring to FIG. 25B, two identical high side circuits are connected in parallel and two identical rectifier circuits are connected in parallel also. The gate drive signals to the high side circuit 1 and high side circuit 2 are phase shifted. The gate drive signals to the rectifier circuit 1 and rectifier circuit 2 are also phase shifted. This arrangement can achieve all the benefits of interleaving.