US012278555B2

# (12) United States Patent Liu et al.

### (54) VARIABLE GAIN MODULATION METHODS AND CONTROLLERS FOR AC-DC CONVERTER WITH POWER FACTOR CORRECTION

(71) Applicant: Queen's University at Kingston,

Kingston (CA)

(72) Inventors: Yan-Fei Liu, Kingston (CA); Binghui

He, Kingston (CA); Yang Chen, Hefei (CN); Bo Sheng, Kanata (CA); Wenbo

Liu, Shenzhen (CN)

(73) Assignee: Queen's University at Kingston,

Kingston (CA)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 259 days.

Appl. No.: 17/973,616

(22) Filed: Oct. 26, 2022

(65) Prior Publication Data

US 2023/0126710 A1 Apr. 27, 2023

#### Related U.S. Application Data

- (60) Provisional application No. 63/272,154, filed on Oct. 26, 2021.

- (51) Int. Cl.

#02M 1/15 (2006.01)

#02M 1/10 (2006.01)

(Continued)

(Continued)

### (10) Patent No.: US 12,278,555 B2

(45) **Date of Patent:** Apr. 15, 2025

#### (58) Field of Classification Search

CPC .... H02M 1/0022; H02M 1/0048; H02M 1/10; H02M 1/15; H02M 1/42; H02M 1/4208; (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

WO WO-2019144241 A1 \* 8/2019 ....... H02M 3/33576

#### OTHER PUBLICATIONS

M. Chen et al., "Multitrack power factor correction architecture," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 2018, pp. 737-745, doi: 10.1109/APEC.2018.8341094. (Year: 2018).\*

Primary Examiner — Fred E Finch, III (74) Attorney, Agent, or Firm — Stephen J. Scribner

#### (57) ABSTRACT

A controller for an AC-DC converter including a rectifier circuit that converts AC input voltage into DC output voltage uses control logic to control the rectifier circuit according to two or more operating modes. Each operating mode determines a gain of the rectifier circuit. The controller selects an operating mode from the two or more operating modes based on at least one of an AC input voltage value and a required DC output voltage value. The AC-DC converter provides a wide range of DC output voltage with power factor correction. The controller may be used with AC-DC converter topologies such as boost converter, isolated boost converter, PWM converter, LLC resonant converter, and LCC resonant converter.

25 Claims, 26 Drawing Sheets

## US 12,278,555 B2

Page 2

(51) **Int. Cl. H02M 1/42** (2007.01) **H02M 3/00** (2006.01)

H02M 3/335 (2006.01)

(52) U.S. Cl. CPC .... H02M 3/33571 (2021.05); H02M 3/33573

(58) Field of Classification Search

CPC ....... H02M 1/4225–4258; H02M 3/01; H02M

3/33571; H02M 3/33573

See application file for complete search history.

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 2017/0016655 A1* | 1/2017  | Shinomoto H02M 1/4225 |

|------------------|---------|-----------------------|

| 2017/0063225 A1* | 3/2017  | Guo H02M 3/158        |

| 2021/0021207 A1* | 1/2021  | Choi H02M 7/2176      |

| 2021/0367522 A1* | 11/2021 | Mao H02M 3/33571      |

| 2022/0158547 A1* | 5/2022  | Lind H02M 1/4233      |

| 2022/0360175 A1* | 11/2022 | Peng H02M 1/0003      |

| 2022/0393574 A1* | 12/2022 | Pervaiz H02M 3/33592  |

| 2023/0111992 A1* | 4/2023  | Liu H02M 1/10         |

|                  |         | 363/21.02             |

<sup>\*</sup> cited by examiner

Fig. 4 (Prior art)

Fig. 6

Fig. 7A

Fig. 7B

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 13

Fig. 14

Fig. 15

Fig. 16

Fig. 17

Fig. 18

Fig. 19

Fig. 21A (Prior art)

Fig. 23 (Prior art)

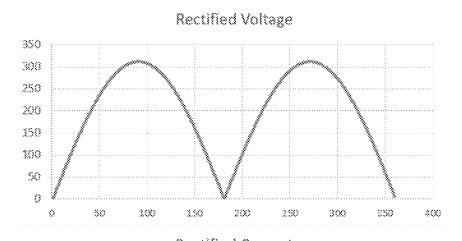

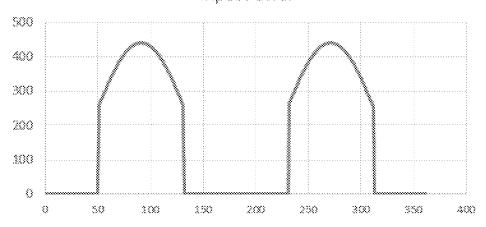

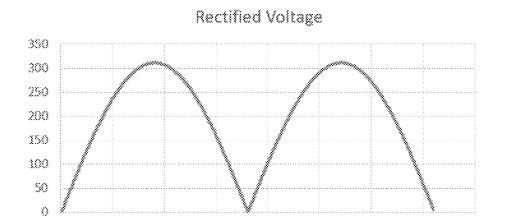

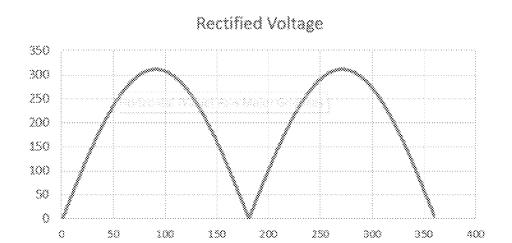

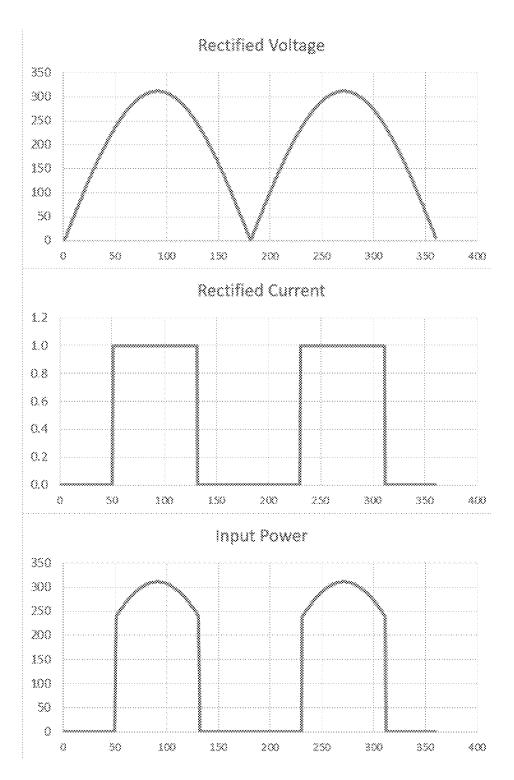

## Rectified Voltage

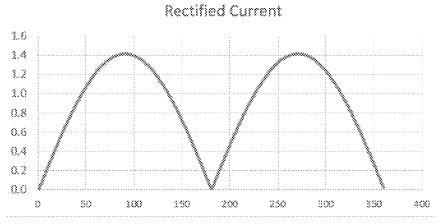

## **Rectified Current**

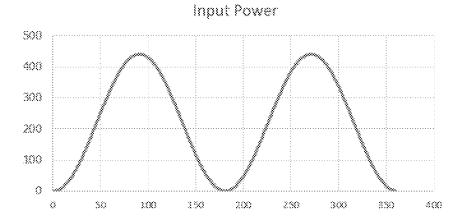

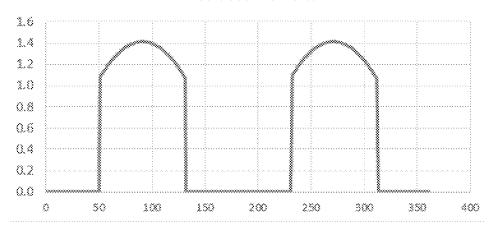

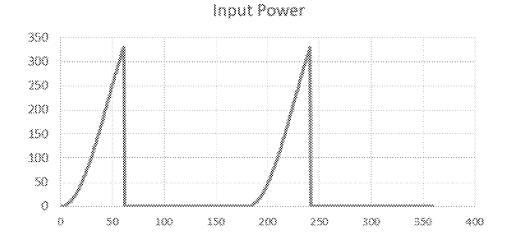

## Input Power

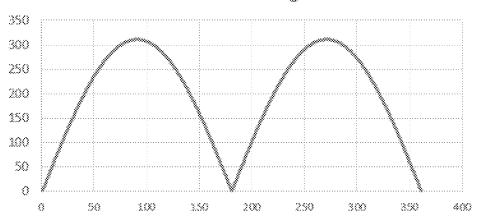

Fig. 24

3.90

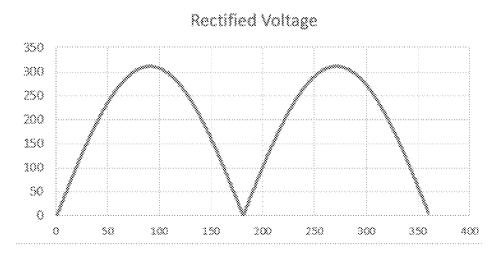

Fig. 25

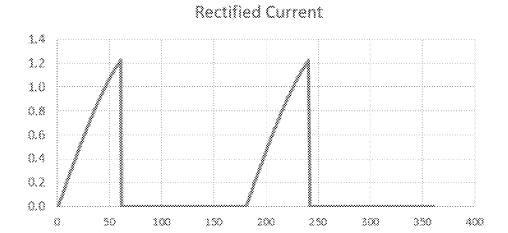

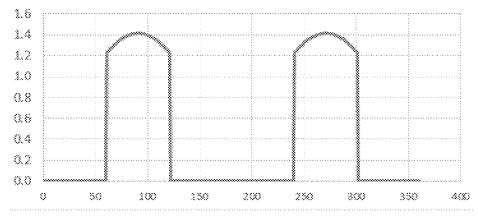

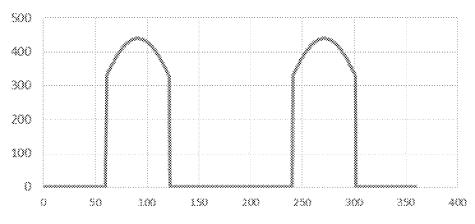

## **Rectified Current**

Input Power

Fig. 26

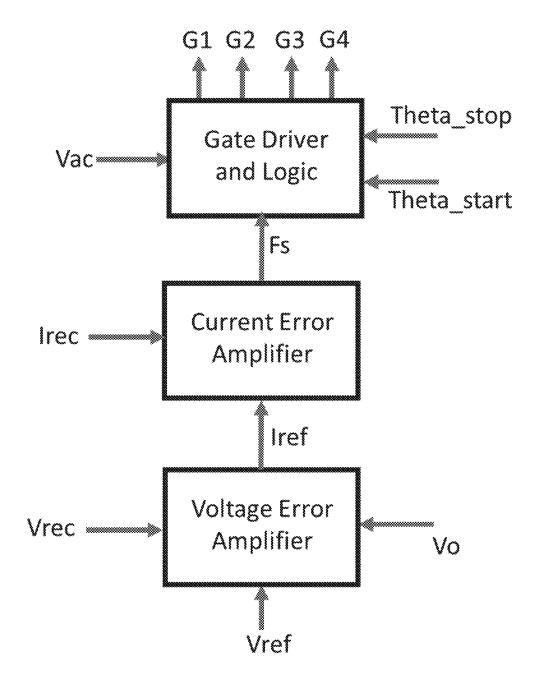

Fig. 27

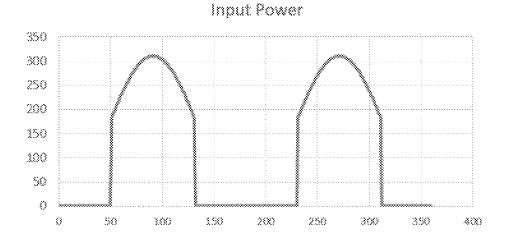

#### **Rectified Current** 1.2 1.0 8.8 8.8 0.4 0.2 0.0 8 50 100 300 250 300 350 350 400

Fig. 28

Fig. 29

#### VARIABLE GAIN MODULATION METHODS AND CONTROLLERS FOR AC-DC CONVERTER WITH POWER FACTOR CORRECTION

#### RELATED APPLICATION

This application claims the benefit of the filing date of Application No. 63/272,154, filed on Oct. 26, 2021, the contents of which are incorporated herein by reference in  $^{10}$ their entirety.

#### **FIELD**

The invention relates generally to the field of AC-DC 15 converters. More specifically, the invention relates to controllers and control methods for AC-DC converters that implement two or more operating modes, wherein each operating mode determines a gain of the converter rectifier circuit and the AC-DC converter provides a wide range of 20 gain mode, low-gain mode, and zero-gain mode. DC output voltage with power factor correction.

#### BACKGROUND

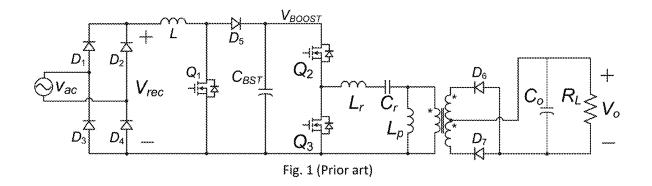

rectifier to achieve power factor correction. The output voltage of a boost converter will be higher than the peak value of the input AC voltage. For common applications, the AC voltage is changed from 90V to 264V to cover both 120V (60 Hz) AC system and 220V (50 Hz) AC voltage 30 system. Therefore, the output voltage of the boost converter is usually regulated at 400V. Since (1) the load will generally require a voltage different from the boost output voltage (e.g., 400V), and (2) the load will require electrical isolation from the AC voltage, another DC-DC converter is needed to 35 convert the 400V boost output voltage to the output voltage, Vout. FIG. 1 shows a typical circuit diagram to achieve this objective according to a prior approach. The capacitor CBST is used as an energy storage capacitor that stores the energy to buffer the pulsating input power from AC source. It 40 contains an average voltage (DC voltage) of around 400V plus a double line frequency ripple (120 Hz for 60 Hz AC line and 100 Hz for 50 Hz line). The double line frequency ripple voltage is usually around 10 to 20V peak, depending on the design.

In some applications, the variation of the AC input voltage is large, such as from 90V to 264V, a 3:1 variation ratio. The variation of the output voltage is also large. For example, if the circuit of FIG. 1 is used to charge the battery of an electric vehicle (EV), the battery voltage will change from 50 250V (when the battery is fully discharged) to 430V (when the battery is fully charged). Therefore, when the input voltage is at the lowest level, such as 90V and the output voltage is at the highest level, such as 430V, the voltage gain is calculated as Vgain\_max=430V/90V=4.8. When the input 55 voltage is at the highest level, such as 264V and the output voltage is at the lowest level, such as 250V, the voltage gain is calculated as Vgain\_min=250V/264V=0.95. In order to meet the EV battery charge requirement, the voltage gain of the EV charger will have a variation range of 4.8/0.95=5, 60 which is a very large range. The prior approach can only achieve optimal performance at a very narrow range. For example, when input voltage is 220V, output battery voltage is between 330V to 380V, the power supply will achieve highest efficiency operation. When the input voltage and 65 battery voltage is outside this range, the efficiency of the EV charger is significantly lower. Therefore the prior approach

2

cannot achieve optimal performance over a wide voltage variation range, when the input voltage and output voltage have a large variation, such as described above.

#### **SUMMARY**

According to one aspect of the invention there is provided a controller for an AC-DC converter comprising a rectifier circuit that converts AC input voltage into DC output voltage, the controller comprising: control logic that controls the rectifier circuit according to two or more operating modes; wherein each operating mode of the two or more operating modes determines a gain of the rectifier circuit; wherein the controller selects an operating mode from the two or more operating modes based on at least one of an AC input voltage value and a required DC output voltage value; wherein the AC-DC converter provides a wide range of DC output voltage with power factor correction.

In one embodiment the operating modes include high-

In one embodiment the high-gain mode, low-gain mode, and zero-gain mode are alternatively implemented by the controller.

In one embodiment the controller controls the rectifier A boost converter is commonly used as the AC-DC 25 circuit to operate in first and second modes; wherein the rectifier circuit operates in the first mode for a first integer value of a half-line period of the AC input voltage and the rectifier circuit operates in the second mode for a second integer value of the half-line period of the AC input voltage.

> In one embodiment the DC output voltage contains a ripple voltage with a ripple frequency lower than an AC line frequency.

In one embodiment an LLC converter is used as the rectifier circuit.

In one embodiment the controller controls the rectifier circuit according to full-bridge operating mode, half-bridge operating mode, and non-operating mode; wherein the rectifier circuit is full-bridge operating mode for a first integer value of a half-line period of the AC input voltage; wherein the rectifier circuit is in half-bridge operating mode for a second integer value of the half-line period of the AC input line voltage; wherein the rectifier circuit is in non-operating mode for a third integer value of the half-line period of the AC input voltage.

In one embodiment the DC output voltage of the AC-DC converter contains a low frequency ripple voltage; wherein a frequency of the ripple voltage is related to the frequency of the AC input line voltage.

In one embodiment the rectifier circuit is in full-bridge mode when the input AC voltage is in a low range; the rectifier circuit is in half-bridge mode when the input AC voltage is in a high-range; the output DC voltage is regulated to a required DC value by changing the gain of the rectifier circuit in the full-bridge mode when input voltage is in the low range; the output DC voltage is regulated to the required DC value by changing the gain of the rectifier circuit in the half-bridge mode when input AC voltage is in the high range.

In one embodiment the output DC voltage is regulated to the required value by alternatingly operating the rectifier circuit between full-bridge mode and half-bridge mode when input AC voltage is between the low range and the high range.

In one embodiment the rectifier circuit operates in fullbridge mode for one integer value of the half-line period of the AC input voltage and stops operating for another integer value of half-line period of the AC input voltage.

3

In one embodiment the output DC voltage is regulated to the required value by changing the gain of the rectifier circuit when it is operating in full-bridge mode.

In one embodiment the output DC voltage is regulated to the required value by changing a ratio of the first and second 5 integer values.

In one embodiment the output DC voltage is regulated to the required value by a combination of changing the gain of the rectifier circuit and changing of ratio of the first and second integer values.

In one embodiment the rectifier circuit operates in halfbridge mode for a first integer value of the half-line period of the AC input voltage and stops operating for a second integer value of the half-line period of the AC input voltage.

In one embodiment the output DC voltage is regulated to 15 the required value by changing the gain of the rectifier circuit operating in half-bridge mode.

In one embodiment the controller controls the rectifier circuit so that the rectifier circuit is operating for a first portion of the AC input voltage half line period and the 20 rectifier circuit is not operating for a second portion of the AC input voltage half line period.

In one embodiment the rectifier circuit is operating when an instantaneous AC input voltage is at or close to its peak value and the rectifier circuit is not operating when the 25 used as the rectifier circuit. In one embodiment of the crossing value.

an AC line frequency.

In one embodiment of the used as the rectifier circuit. In one embodiment of the the rectifier circuit according

In one embodiment the rectifier circuit is operating when an instantaneous AC input voltage is at its peak value±45 degrees and the rectifier circuit is not operating when the 30 instantaneous AC input voltage is at its zero-crossing value±45 degrees.

In one embodiment the output DC voltage is regulated by controlling AC input power to the rectifier circuit during a time interval when the rectifier circuit is operating.

In one embodiment the output DC voltage is regulated by controlling a duration of a time interval when the rectifier circuit is operating.

In one embodiment the rectifier circuit is operating during a first portion of the AC input voltage half line cycle when 40 an instantaneous AC input voltage is substantially different from an AC input peak voltage value and the rectifier circuit is not operating for the rest of the AC input voltage half line cycle.

In one embodiment the rectifier circuit is operating during 45 a first portion of the AC input voltage half line cycle when an instantaneous AC input voltage is from 0 to 45 degrees or from 135 to 180 degrees from an AC input peak voltage value and the rectifier circuit is not operating for the rest of the AC input voltage half line cycle.

In one embodiment the controller is implemented at least in part in computer-executable instructions stored on nontransitory computer-readable storage media, and the controller includes a computer or other processor that executes the stored instructions.

According to another aspect of the invention there is provided an AC-DC converter comprising a controller in accordance with embodiments described herein.

The AC-DC converter may be a boost converter, isolated boost converter, PWM converter, LLC resonant converter, 60 or LCC resonant converter.

According to another aspect of the invention there is provided a method for controlling an AC-DC converter, comprising using a controller comprising control logic to control a rectifier circuit of the AC-DC converter according to two or more operating modes; wherein each operating mode of the two or more operating modes determines a gain

4

of the rectifier circuit; wherein the controller selects an operating mode from the two or more operating modes based on at least one of an AC input voltage value and a required DC output voltage value; wherein the AC-DC converter provides a wide range of DC output voltage with power factor correction.

In one embodiment of the method the operating modes include high-gain mode, low-gain mode, and zero-gain mode.

In one embodiment of the method the high-gain mode, low-gain mode, and zero-gain mode are alternatively implemented by the controller.

In one embodiment of the method the controller controls the rectifier circuit to operate in first and second modes; wherein the rectifier circuit operates in the first mode for a first integer value of a half-line period of the AC input voltage and the rectifier circuit operates in the second mode for a second integer value of the half-line period of the AC input voltage.

In one embodiment of the method the DC output voltage contains a ripple voltage with a ripple frequency lower than an AC line frequency.

In one embodiment of the method an LLC converter is used as the rectifier circuit.

In one embodiment of the method the controller controls the rectifier circuit according to full-bridge operating mode, half-bridge operating mode, and non-operating mode; wherein the rectifier circuit is full-bridge operating mode for a first integer value of a half-line period of the AC input voltage; wherein the rectifier circuit is in half-bridge operating mode for a second integer value of the half-line period of the AC input line voltage; wherein the rectifier circuit is in non-operating mode for a third integer value of the half-line period of the AC input voltage.

In one embodiment of the method the DC output voltage of the AC-DC converter contains a low frequency ripple voltage; wherein a frequency of the ripple voltage is related to the frequency of the AC input line voltage.

In one embodiment of the method the rectifier circuit is in full-bridge mode when the input AC voltage is in a low range; the rectifier circuit is in half-bridge mode when the input AC voltage is in a high-range; the output DC voltage is regulated to a required DC value by changing the gain of the rectifier circuit in the full-bridge mode when input voltage is in the low range; the output DC voltage is regulated to the required DC value by changing the gain of the rectifier circuit in the half-bridge mode when input AC voltage is in the high range.

In one embodiment of the method the output DC voltage is regulated to the required value by alternatingly operating the rectifier circuit between full-bridge mode and half-bridge mode when input AC voltage is between the low range and the high range.

In one embodiment of the method the rectifier circuit operates in full-bridge mode for one integer value of the half-line period of the AC input voltage and stops operating for another integer value of half-line period of the AC input voltage.

In one embodiment of the method the output DC voltage is regulated to the required value by changing the gain of the rectifier circuit when it is operating in full-bridge mode.

In one embodiment of the method the output DC voltage is regulated to the required value by changing a ratio of the first and second integer values.

In one embodiment of the method the output DC voltage is regulated to the required value by a combination of

changing the gain of the rectifier circuit and changing of ratio of the first and second integer values.

In one embodiment of the method the rectifier circuit operates in half-bridge mode for a first integer value of the half-line period of the AC input voltage and stops operating for a second integer value of the half-line period of the AC input voltage.

In one embodiment of the method the output DC voltage is regulated to the required value by changing the gain of the rectifier circuit operating in half-bridge mode.

In one embodiment of the method the controller controls the rectifier circuit so that the rectifier circuit is operating for a first portion of the AC input voltage half line period and the rectifier circuit is not operating for a second portion of the AC input voltage half line period.

In one embodiment of the method the rectifier circuit is operating when an instantaneous AC input voltage is at or close to its peak value and the rectifier circuit is not operating when the instantaneous AC input voltage is at or close to its zero-crossing value.

In one embodiment of the method the rectifier circuit is operating when an instantaneous AC input voltage is at its peak value±45 degrees and the rectifier circuit is not operating when the instantaneous AC input voltage is at its zero-crossing value±45 degrees.

In one embodiment of the method the output DC voltage is regulated by controlling AC input power to the rectifier circuit during a time interval when the rectifier circuit is operating.

In one embodiment of the method the output DC voltage <sup>30</sup> is regulated by controlling a duration of a time interval when the rectifier circuit is operating.

In one embodiment of the method the rectifier circuit is operating during a first portion of the AC input voltage half line cycle when an instantaneous AC input voltage is substantially different from an AC input peak voltage value and the rectifier circuit is not operating for the rest of the AC input voltage half line cycle.

In one embodiment of the method the rectifier circuit is operating during a first portion of the AC input voltage half 40 line cycle when an instantaneous AC input voltage is from 0 to 45 degrees or from 135 to 180 degrees from an AC input peak voltage value and the rectifier circuit is not operating for the rest of the AC input voltage half line cycle.

In various embodiments of the method the AC-DC converter may be a boost converter, isolated boost converter, PWM converter, LLC resonant converter, or LCC resonant converter.

According to another aspect of the invention there is provided non-transitory computer readable media for use 50 with a processor, the computer readable media having stored thereon instructions that direct the processor to execute processing steps including controlling a rectifier circuit of an AC-DC converter in accordance with embodiments described herein.

### BRIEF DESCRIPTION OF THE DRAWINGS

For a better understanding of the invention, and to show more clearly how it may be carried into effect, embodiments 60 will be described, by way of example, with reference to the accompanying drawings, wherein:

FIG. 1 is a circuit diagram of a boost converter followed by a LLC converter for an AC-DC power supply, according to the prior art.

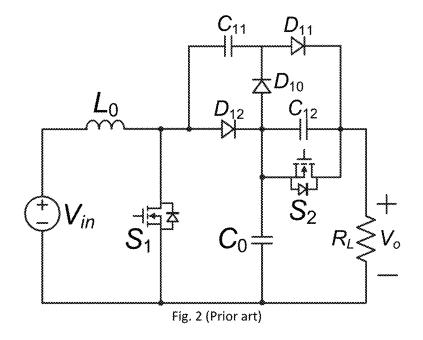

FIG. 2 is a circuit diagram of a boost converter with voltage doubler, according to the prior art.

6

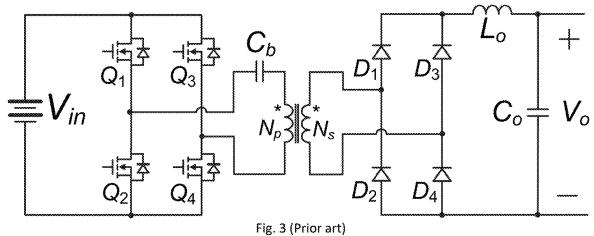

FIG. 3 is a circuit diagram of a full-bridge pulse width modulation (PWM) converter, according to the prior art.

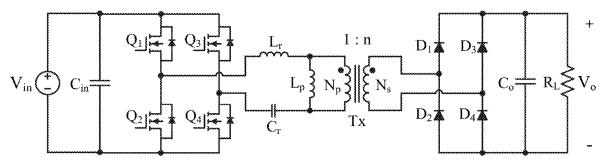

FIG. 4 a circuit diagram of a full-bridge LLC DC-DC converter, according to the prior art.

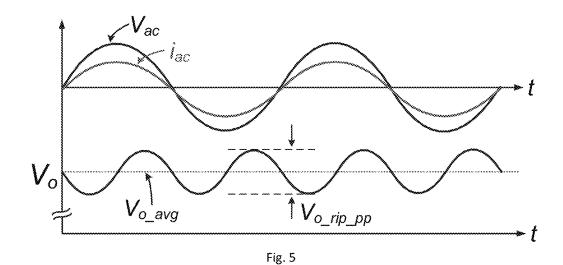

FIG. 5 is a plot of AC input voltage, AC input current, and output voltage waveforms of an AC to DC converter with power factor correction (PFC), according to the prior art.

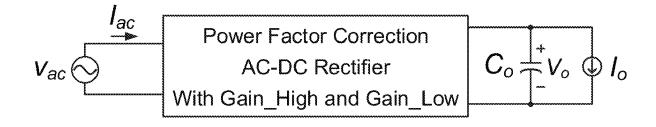

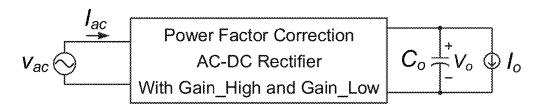

FIG. 6 is generalized circuit block diagram of an AC-DC rectifier with power factor correction showing the output hold up capacitor and constant current load, according to one embodiment.

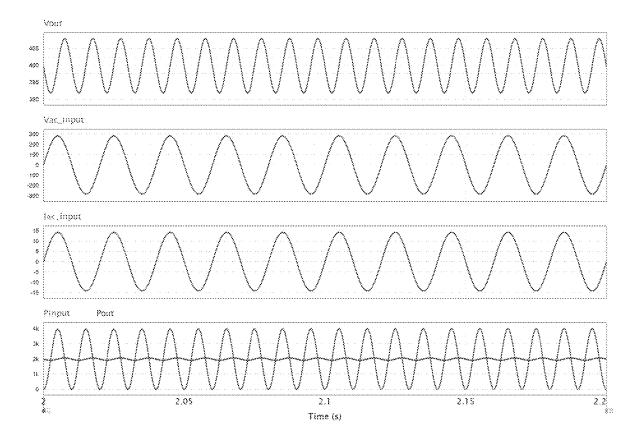

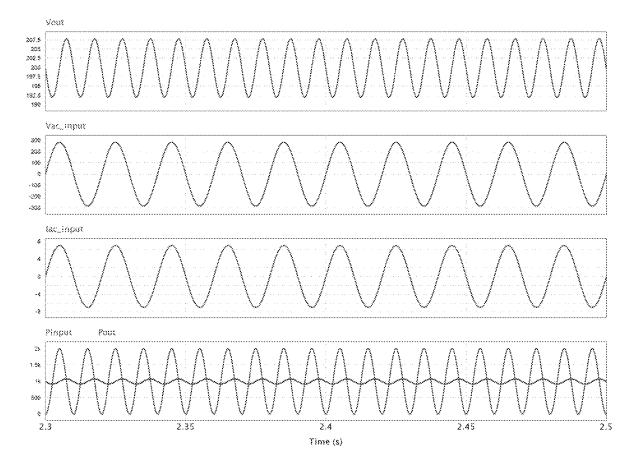

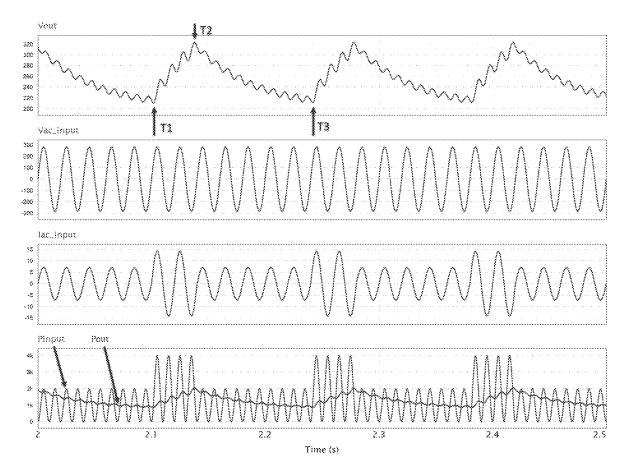

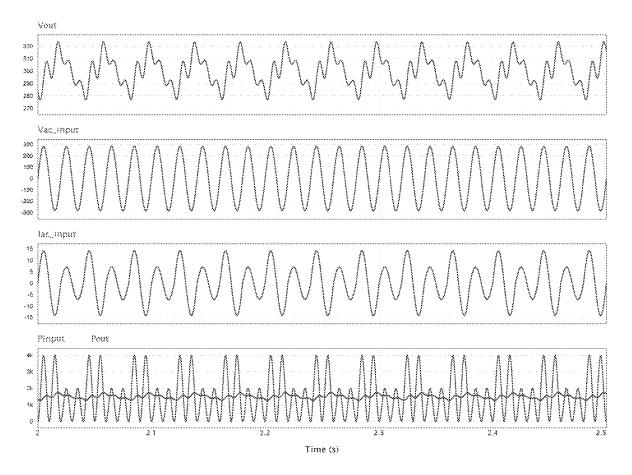

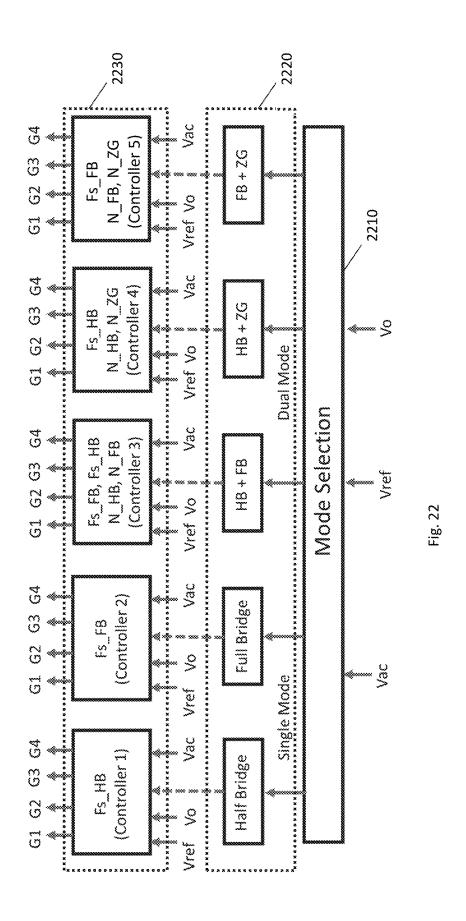

FIGS. 7A and 7B are simulation waveforms of an embodiment at normal operation at high-gain mode Vo\_avg=400V, Vo\_rip\_pp=16V, Pout=2,000 W and at low gain mode, Vo\_avg=200V, Vo\_rip\_pp=16V, Pout=1,000 W, respectively.

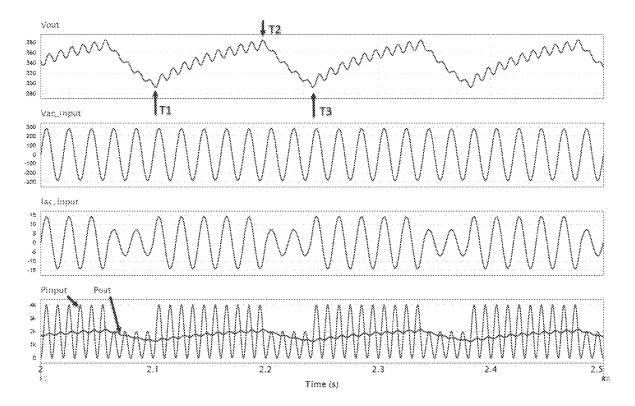

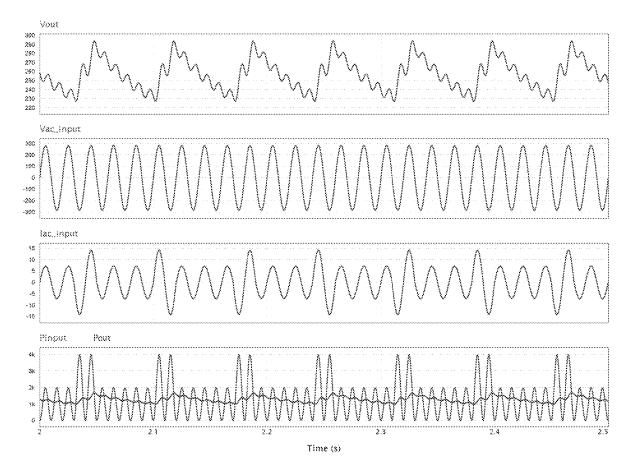

FIG. **8** shows simulation waveforms for sub-line frequency modulation, wherein N\_high=5, N\_low=2, Vo\_avg=342.7V, Vo\_rip\_pp=92V, Pout=1,721 W, according to one embodiment.

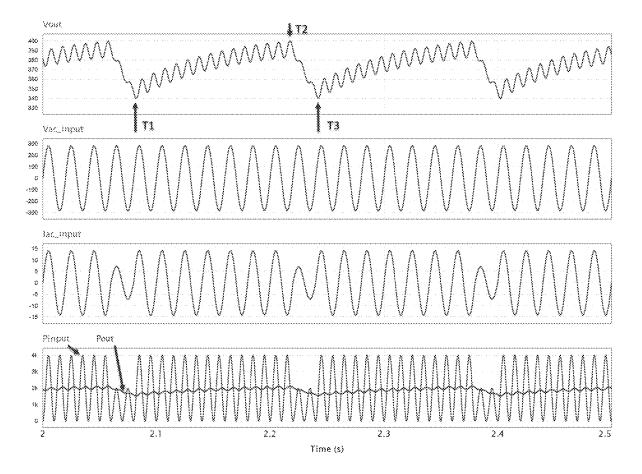

FIG. **9** shows simulation waveforms for sub-line frequency modulation with N\_high=7, N\_low=1, Vo\_avg=375V, Vo\_rip\_pp=60V, Pout=1,876 W, according to one embodiment.

FIG. 10 shows simulation waveforms for sub-line frequency modulation with N\_high=2, N\_low=2, Vo\_avg=300V, Vo\_rip\_pp=78V, Pout=1,500 W, according to one embodiment.

FIG. 11 shows simulation waveforms for sub-line frequency modulation with N\_high=2, N\_low=5, Vo\_avg=257V, Vo\_rip\_pp=112V, Pout=1,302 W, according to one embodiment.

FIG. 12 shows simulation waveforms for sub-line frequency modulation with N\_high=5, N\_low=2, and Gain\_high=2, Gain\_low=1.04, Vo\_avg=345V, Vo\_rip\_pp=88.8V, Pout=1,732 W, according to one embodiment.

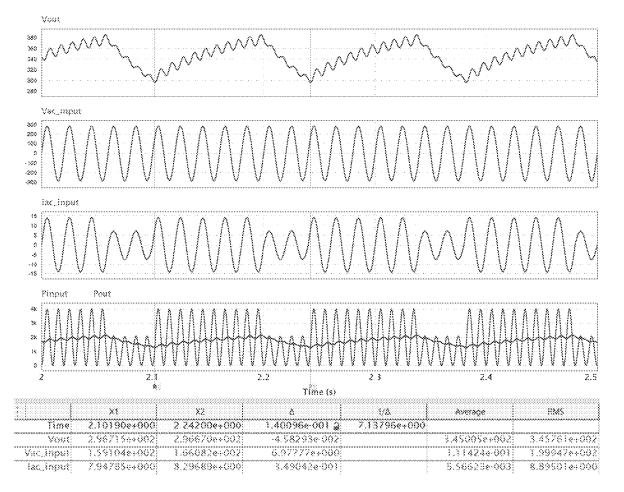

FIG. 13 shows simulation waveforms for sub-double line frequency modulation, N\_half\_high=5, N\_half\_low=2, Vo\_avg=342.7V, Vo\_rip\_pp=55V, and Pout=1,716 W, according to one embodiment.

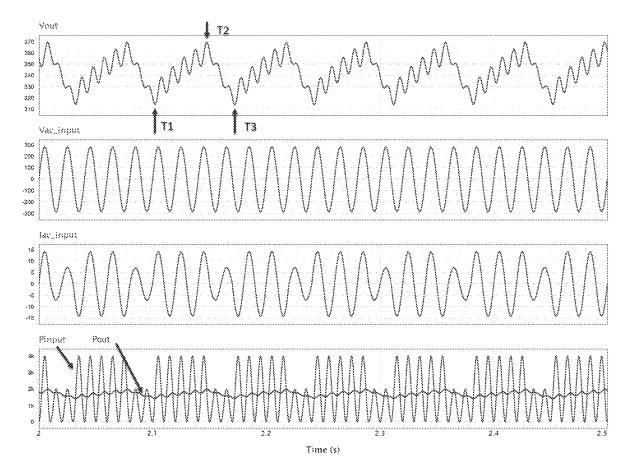

FIG. 14 shows simulation waveforms for sub-double line frequency modulation, N\_half\_high=7, N\_half\_low=1, Vo\_avg=375V, Vo\_rip\_pp=38V, and Pout=1,875 W, according to one embodiment.

FIG. 15 shows simulation waveforms for sub-double line frequency modulation, N\_half\_high=2, N\_half\_low=2, Vo\_avg=300V, Vo\_rip\_pp=38V, and Pout=1,502 W, according to one embodiment.

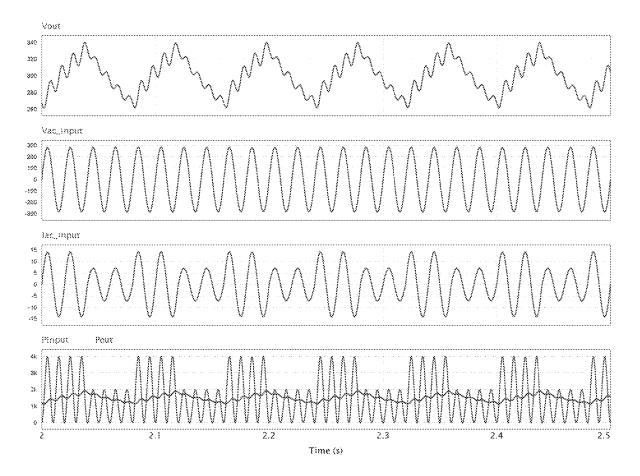

FIG. **16** shows simulation waveforms for sub-double line frequency modulation, N\_half\_high=2, N\_half\_low=5, Vo\_avg=275V, Vo\_rip\_pp=66V, and Pout=1,290 W, according to one embodiment.

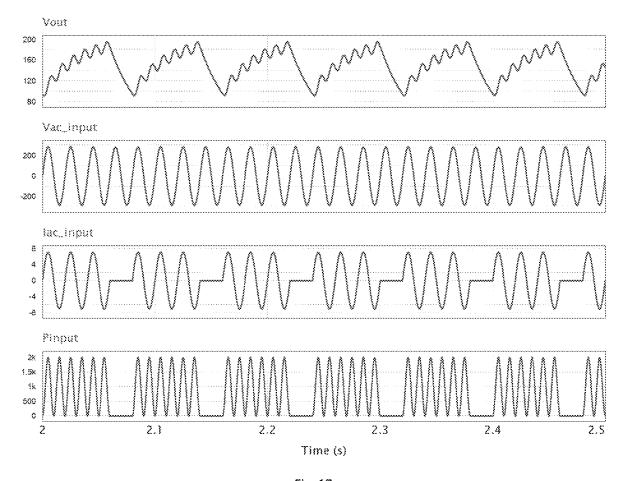

FIG. 17 shows simulation waveforms for sub-line frequency modulation, N\_half\_low=6, N\_half\_zero=2, Vo\_avg=150V, Vo\_rip\_pp=55V, and Pin\_avg=750 W, according to one embodiment.

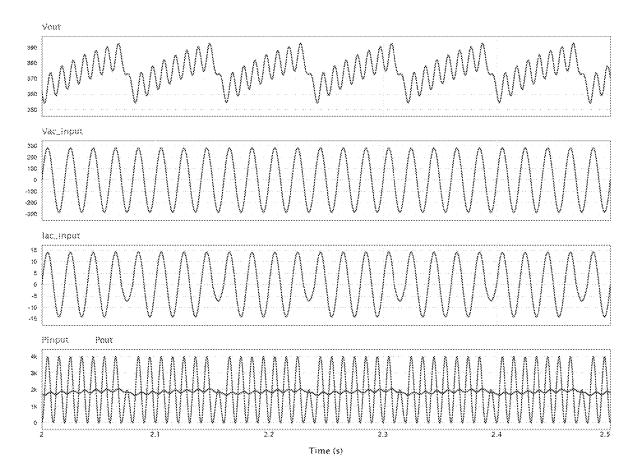

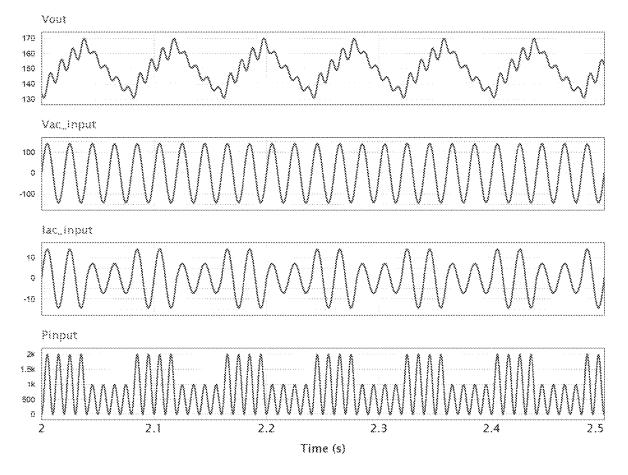

FIG. 18 shows simulation waveforms for sub-double-Line frequency modulation, N\_half\_high=4, N\_half\_low=4, Vin=100V, Vo\_avg=150V, Vo\_rip\_pp=39V, Pin\_avg=750 W, and R\_load=300, according to one embodiment.

FIG. 19 shows simulation waveforms for sub-double-line frequency modulation, wherein N\_half\_high=2, N\_half\_low=6, Vin=120V, Vo\_avg=150V, Vo\_rip\_pp=35V, Pin\_avg=750 W, and R\_load=300, according to one embodiment.

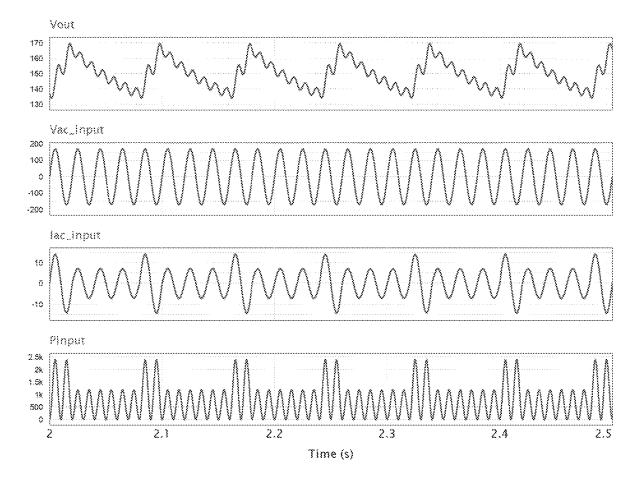

FIG. 20 shows simulation waveforms for sub-double-line frequency modulation, wherein N\_half\_low=6, N\_half\_

zero=2, Vin=200V, Vo\_avg=150V, Vo\_rip\_pp=55V, Pin\_avg=750 W, and R\_load=300, according to one embodiment.

FIG. **21**A is a circuit diagram of an LLC converter that may be used as an AC-DC rectifier with power factor <sup>5</sup> correction, according to the prior art.

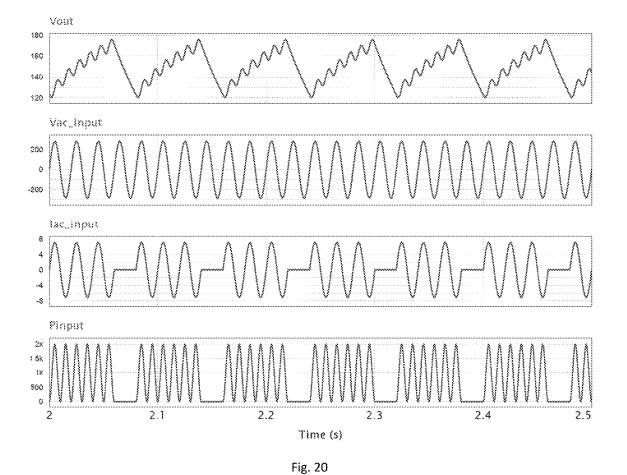

FIG. **21**B is a control block diagram for controlling an LLC converter to achieve PFC operation.

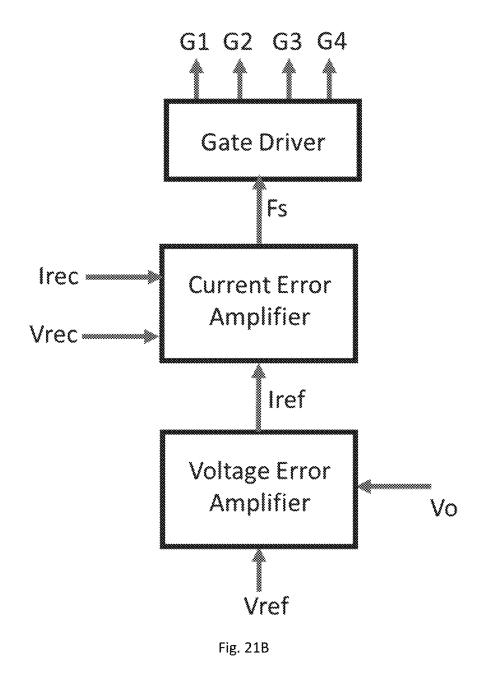

FIG. 22 is a control block diagram for an AC-DC rectifier, according to one embodiment.

FIG. 23 shows waveforms for an LLC converter under conventional control in PFC mode, wherein the x-axes are degrees, and the rectified input voltage (top), current (middle), and input power (bottom) waveforms are shown, according to the prior art.

FIG. 24 shows waveforms for inner-line frequency modulation implemented for an LLC converter wherein the converter is on from 50-degree to 130-degree, according to one embodiment.

FIG. **25** shows waveforms for inner-line frequency modulation implemented for an LLC converter, according to one embodiment.

FIG. 26 shows waveforms for inner-line frequency modulation implemented for an LLC converter, wherein the converter is on from 60-degree to 120-degree, according to 25 one embodiment.

FIG. 27 shows waveforms for inner-line frequency modulation when current is controlled to be constant, according to one embodiment.

FIG. 28 shows waveforms for inner-line frequency modulation with peak current of 1 A, reduced from 1.4 A, according to one embodiment.

FIG. 29 is a control block diagram for an inner-line frequency modulation control strategy, according to one embodiment.

#### DETAILED DESCRIPTION OF EMBODIMENTS

## 1 Switching Converters with Two or More Operating Modes

Described herein are controllers and circuits for an AC-DC rectifier for applications with large input and output voltage variation range, wherein the AC-DC rectifier has two or more voltage gains and the AC-DC rectifier performs 45 under optimal operating condition over the entire input and output voltage variation range.

Accordingly, embodiments provide a power converter that has two or more operating mode and produces two or more voltage gains, both or all of which achieve optimal 50 operation (such as high efficiency operation), and a method for controlling the input power of the power converter so that the output power may be controlled over a wide range and the power converter is always operating at optimal condition, that is, at high efficiency or the most efficient 55 condition when the converter is producing different (e.g., high or low) output power. According to embodiments, the control method is applied to the AC input and the input AC current follows the shape of the AC voltage to achieve power factor correction. The control method may be used to select 60 the operation mode to achieve power factor correction over wide input voltage variation range and output voltage variation range and at different power levels, so that the power converter maintains high efficiency operation in the two or more operating modes. The output DC voltage contains low frequency ripple that is approximately two times the AC line frequency. The input AC side and output DC side have

8

electrical isolation. The input voltage variation range may at least a 2:1 ratio. For example, in one embodiment the input voltage variation range may be a 3:1 ratio, e.g., from about 90V to about 264V.

As used herein, the terms "converter", "switching converter", "power converter", "AC-DC converter", "rectifier", and "AC-DC rectifier" are used interchangeably and refer to a converter based on a topology such as, but not limited to, boost, PWM converters, full-bridge, half-bridge, LLC, LCL, and resonant converters. The terms "rectifier" and "AC-DC rectifier" may be used when the input to the converter is an AC voltage.

As used herein, the terms "control" and "controller" are used interchangeably and may refer to control algorithms 15 (e.g., logic, computer software stored on non-transient computer readable media) and/or circuits (e.g., logic circuits, electronic hardware).

As used herein, the term "substantially" as used with respect to a value or condition refers to a value or condition that is the same as, or close to a desired or selected value or condition, as may be achieved within tolerances of circuit components, control parameters, etc. By using the term "substantially" it is understood that a recited characteristic, parameter, and/or value need not be achieved exactly, but that deviations or variations, including for example, tolerances, measurement error, measurement accuracy limitations and other factors known to those of ordinary skill in the art, may occur in amounts that do not preclude the effect the characteristic, parameter, and/or value was intended to provide. A characteristic, parameter, and/or value that is substantially absent (e.g., substantially removed, substantially zero) may be one that is within the noise, beneath background, below detection limits, or a small fraction (e.g., <1%, <0.1%, <0.01%, <0.001%, <0.00001%, <0.000001%, 35 <0.000001%) of the significant characteristic. It is understood that a characteristic, parameter, and/or value that is referred to herein as being the "same" as another characteristic, parameter, and/or value may be substantially the same as the other characteristic, parameter, and/or value.

Simulations described herein were conducted using PSIM Professional version 2021b.1.7 (Powersim Inc., Troy, MI, USA).

A controller may be implemented to control operation of the converter, which may include implementing a gain modulation strategy as described herein. The controller may perform one or more operations such as, for example, but not limited to, input and/or output voltage and/or current sensing, generating voltage and/or current reference signals, power factor correction, and generating gate drive signals for switches (e.g., MOSFETs, IGBTs, etc.) of the converter.

The controller may include an electronic processor and a memory. The processor may be, for example, a computer, or a digital controller such as a microcontroller unit (MCU), field programmable gate array (FPGA), etc. The processor may include processing capabilities as well as an input/ output (1/O) interface through which the processor may receive a plurality of input signals (e.g., voltage and/or current sensing signals, voltage and/or current reference signals), and generate a plurality of output signals (e.g., gate drive signals for switches of the converter). The memory is provided for storage of data and instructions or code (i.e., an algorithm, such as a controller algorithm, controller logic, software, etc.) executable by the processor. The memory may include various forms of non-volatile (i.e., non-transitory) memory including flash memory or read only memory (ROM) including various forms of programmable read only memory (e.g., PROM, EPROM, EEPROM) and/or volatile

memory including random access memory (RAM) including static random access memory (SRAM), dynamic random access memory (DRAM) and synchronous dynamic random access memory (SDRAM). A converter may include a driver circuit or device to interface between outputs of the controller and the control (e.g., gate) terminals of the semiconductor switches.

The memory stores executable code including control logic which is configured to control the overall operation of a converter in accordance with a desired control strategy, such as a converter gain modulation strategy as described herein. For example, the control logic, when executed by the processor, is configured to generate, in response to one or more input signals, the various gate drive signals for the switches of the converter. The control logic may include programmed logic blocks to implement specific functions, for example, including without limitation, zero crossing detection, error amplifier, pulse width modulation (PWM), power factor correction (PFC), zero voltage switching (ZVS), rms voltage and/or current calculator, operating 20 mode control logic, and startup and/or shut down strategy. The memory may also store features, e.g., a lookup table that may be accessed by the control logic. Non-limiting examples of control strategies, or parts thereof, that may be implemented separately or in various combinations in controllers according to embodiments described herein are shown in FIGS. 21B, 22, 29, and/or to control strategies for a rectifier circuit to achieve performance characteristics such as, but not limited to, those shown by example in waveforms of FIGS. 7A, 7B, 8-20, and 24-28.

Control methods described herein may implement at least one modulation strategy. In one embodiment, a modulation strategy includes changing the voltage gain from one AC line cycle to the next AC line cycle, referred to herein as sub-line frequency modulation, or as sub-F\_line modulation. This may include changing the operation mode of the converter at a frequency lower than the line frequency (or AC line frequency, 50 Hz in Asia, Europe and 60 Hz in North America). Operation modes may include high voltage gain, low voltage gain, and zero voltage gain. The sub-F\_line modulation frequency (F\_lineM) is lower than the AC line frequency, such as 10 Hz or 20 Hz.

In another embodiment, a modulation strategy includes changing the voltage gain from one half line cycle to the next half line cycle, referred to herein as half line frequency modulation.

In another embodiment, a modulation strategy includes <sup>45</sup> changing the voltage gain within a half AC line cycle, referred to herein as inner-half line cycle modulation.

In another embodiment, referred to as sub-switching frequency modulation, or sub-Fs modulation, the operation mode of the converter is changed at a frequency that is lower than the switching frequency and higher than the AC line frequency. For example, the line frequency may be 50 Hz or 60 Hz, and the switching frequency may be 500 kHz. The sub-Fs modulation frequency (F\_SM) may be, e.g., about 20 kHz. During the sub-Fs modulation period, T\_SM, the converter operates according to one of three possible modes: high voltage gain, low voltage gain, and zero voltage gain.

According to embodiments, an energy storage component may be used to hold the output voltage at a selected DC level. The energy storage component, for example, a capacitor, delivers additional power to the load when the instantaneous input power is lower than the load power and store the extra power when the instantaneous input power is larger than the load power.

An AC-DC rectifier has been used extensively in industry applications. When the output power is more than 75 W, Power Factor Correction (PFC) is required. With PFC, the input AC current is controlled to be the shape and same

10

phase as the input AC voltage. In practical application, the AC voltage is a sinusoidal waveform. Therefore, the AC current is also a sinusoidal waveform.

A conventional boost converter with voltage doubler is shown in FIG. 2. When the capacitor C12 is shorted by a MOSFET S2, the output voltage of the boost converter is:

$$V_{\text{gain\_low}} = V_{\text{boost\_low}} / V_{\text{in}} = 1 / (1 - D)$$

(1)

where D is the duty cycle of the switch S1. When the MOSFET S2 is off, the boost converter operates in voltage doubler mode. The output voltage of the boost converter is:

$$V_{\text{gain\_high}} = V_{\text{boost\_high}} / V_{\text{in}} = 2/(1-D)$$

(2)

By controlling S2 on and off, the VD boost converter can operate at two voltage gains with the same duty cycle. It is noted that in the above example, the VD boost converter has two possible operation modes.

Operation mode #1: When S2 is on and the VD boost converter produces the voltage gain as expressed by equation (1) with duty cycle D, Gain\_low.

Operation mode #2: When S2 is off and the VD boost converter produces the voltage gain as expressed by equation (2) with same duty cycle as in operation mode #1, Gain\_high=2\*Gain\_low.

For a boost converter, it is not desirable to operate at very small duty cycle (such as less than about 30%) or very large duty cycle, such as above about 70%. Therefore, by turning S2 on and off in the VD boost converter as shown in FIG. 2, a very wide operation gain can be achieved while the duty cycle is remains at desirable range (between about 30% and about 70%).

For example, for the conventional boost converter, when D is between 30% and 70%, the voltage gain is changed from

$$Gain1=1/(1-0.3)=1.43$$

(3.1)

to

$$Gain2=1/(1-0.7)=3.33$$

(3.2)

The voltage gain variation range is:

When both operation modes are used, the voltage gain is changed from

Gain1=

$$1/(1-0.3)=1.43$$

, when switch S2 is on (3.4)

to

Gain3=

$$2/(1-0.7)=6.67$$

, when S2 is off, (3.5)

Therefore, the voltage gain variation range is

It is noted that a switching converter such as shown in FIG. 2 can provide two voltage gains with the same operating condition, such as same duty cycle in this case, under two operation modes. In some cases, the term "same operation condition" means similar switching frequency for resonant converters

FIG. 3 is a circuit diagram of a conventional full-bridge PWM converter. In the circuit, capacitor Cb is used to block any possible DC voltage from the full-bridge output. When all four switches Q1, Q2, Q3, and Q4 are switching based on PWM control, the voltage gain can be calculated as:

11

where Np is the number of turns of the primary winding of the transformer and Ns is the number of turns of the secondary winding, and D is the duty cycle.

Another operating mode of the full-bridge PWM converter shown in FIG. 3 is Q3 and Q4 are switched based on 5 PWM control and Q1 is turned off and Q2 is turned on all the time (no switching). Equivalently, under this control the converter operates at half-bridge mode. The voltage gain can be calculated as:

From equation (4) and (5), it is observed that the full-bridge PWM converter can produce two voltage gains with different control strategies when same duty cycle D is used.

FIG. 4 is a circuit diagram of a full-bridge LLC converter according to the prior art. In the figure, Cr, Lr, and Lp are resonant components and Q1, Q2, Q3, and Q4 are the switches of the full-bridge configuration. The secondary side is a full wave rectifier with diode bridge. A half wave 20 rectifier with center tapped transformer can also be used. In addition, a synchronous rectifier (SR) can be used to replace the diodes to reduce the loss of the secondary side circuit. Different secondary side configurations do not impact the control strategies presented herein.

Using Fundamental Harmonic Approximation (FHA) method, the approximate output voltage of the full-bridge LLC converter can be expressed as the following equation:

Gain\_FB\_LLC =

$$\frac{V_o}{V_{in}} = \frac{n}{\sqrt{\left[1 + \frac{1}{K}\left(1 - \frac{1}{fn^2}\right)\right] + Q^2\left(f_n - \frac{1}{fn}\right)^2}}$$

(6)

where the transformer turns ratio (n), series resonant frequency  $(f_p)$ , normalized frequency  $(f_n)$ , inductance ratio (K), and quality factor (Q) are as follows:

$$n = \frac{N_s}{N_p}, \, f_r = \frac{1}{2\pi\sqrt{L_rC_r}}, \, f_n = \frac{f_{sw}}{f_r}, \, K = \frac{L_p}{L_r}, \, Q = \frac{\pi^2\times\sqrt{L_r/C_r}}{8\times n^2\times R_L}$$

Similarly, another operation mode of the full-bridge LLC converter is that Q3 and Q4 operates at switching frequency modulation control. Q1 is turned off and Q2 is turned on all the time (no switching). This converter operates at half-bridge mode. Then the voltage gain can be calculated as:

Gain\_HB\_LLC =

$$\frac{V_o}{V_{in}} = \frac{0.5 * n}{\sqrt{\left[1 + \frac{1}{K}\left(1 - \frac{1}{fn^2}\right)\right] + Q^2\left(f_n - \frac{1}{fn}\right)^2}}$$

(7)

From equation (6) and (7), it is observed that the full-bridge LLC converter, as shown in FIG. 4, can produce two voltage gains using same switching frequency under different operating modes (full-bridge and half-bridge). One is to make the LLC converter operate at full-bridge operation mode and the 60 other is to make the LLC converter operate at half-bridge operation mode.

#### 1 Two Voltage Gains

It is noted from the above discussion that some switching power converters, as those shown in FIGS. 2, 3, and 4, may

12

produce two voltage gains. More specifically, these converters have the following features:

- They have two operating modes which produce two voltage gains using the same control parameter value, such as same duty cycle (for PWM converter, FIGS. 2, 3) or same switching frequency (for resonant converter, FIG. 4). At the same input voltage, they can generate two output voltages with same control parameter value.

- (2) They operate at near optimal operating conditions under both operating modes. The term "optimal" means that the converter will operate with high efficiency, or with low voltage or current stress.

For example, if the duty cycle of a boost converter is about 50%, it can be considered as optimal operating con15 dition. However, if the duty cycle is about 90%, it cannot be considered as optimal operating condition because the voltage and current stress for the switches will be very high.

Similarly, if the switching frequency of an LLC converter is close to its resonant frequency, it can be considered as optimal operating condition. However, if the switching frequency of the LLC converter is much higher than the resonant frequency, such as two or three times the resonant frequency, it cannot be considered as optimal operating condition.

Also, for full-bridge PWM converter and full-bridge LLC converter, if all the MOSFETs are turned off all the time, the converter does not operate, and the output voltage and gain will be zero. This mode of operation is considered as zero-gain mode. For a boost converter, if the MOSFETs are turned off, the output voltage will equal to input voltage and the gain is one (1).

1.1 Sub-Line Frequency Modulation Control Strategy

For an AC-DC rectifier with Power Factor Correction (PFC), the AC input current follows the AC input voltage, in same phase and same shape, as shown in FIG. 5. Since the input power is changing over time and the output load draws constant power, an energy storage component is needed. The energy storage component is usually a large capacitor. For the boost converter as shown in FIG. 1, the energy storage capacitor is  $C_{BST}$ . Since  $C_{BST}$  is usually very large, voltage across C<sub>BST</sub> is a DC value (Vo\_avg) with a small low frequency voltage ripple (Vo\_rip\_pp). The ripple frequency is two times the line frequency (100 Hz or 120 Hz). The value of Vo\_avg is much larger than the value of Vo\_rip\_pp. For example, Vo\_avg may be about 400V and Vo\_rip\_pp may be about 10V to 20V. In order to (a) regulate the output voltage over wide range, and (b) remove the low frequency voltage ripple, a second stage DC-DC converter (the LLC converter as shown in FIG. 1) may be added. Since (a) the output voltage of the boost converter is always higher than the input peak AC voltage, and (b) the voltage gain variation of the LLC is normally limited, the output voltage variation range Vo as shown in FIG. 1, is limited.

Described herein is a control technology, referred to as Variable Gain Modulation control, to achieve very wide output voltage variation while maintaining desired, or optimal, operating conditions for the switching converter (also referred to as an AC-DC rectifier when the input is an AC voltage).

Features of Variable Gain Modulation include:

(1) A switching power converter that operates under two or more voltage gain modes, such as high-gain operating mode (with gain value of Gain\_high) and lowgain operating mode (with gain value of Gain\_low), is used to convert an AC voltage to a DC voltage. The switching converter may also achieve Power Factor Correction (PFC).

- (2) An energy storage capacitor at the output of the switching power converter to maintain approximately DC voltage across the load.

- (3) The switching power converter operates at optimal or near optimal conditions (such as high efficiency operation) for both high-gain mode and low-gain mode operation.

- (4) The switching power converter may operate at high-gain mode and low-gain mode alternatively based on period of line cycle, such as 20 ms for 50 Hz system and 16.67 ms for 60 Hz system. For example, the converter may operate at high-gain mode for N\_high AC line cycles followed by operating at low-gain mode for N\_low AC line cycles (where N\_high and N\_low are integers), and then returns to high-gain operating mode.

- (5) The output DC voltage contains a DC component and a low frequency ripple component. The frequency of the low frequency component depends on N\_high and N\_low, as well as the period of the AC voltage (T\_line). For 50 Hz AC system, T\_line=20 ms. If the converter operates at high-gain mode for two AC line cycles (N\_high=2) and operates at low-gain mode for three AC line cycles (N\_low=3), then the output voltage ripple will contain a low ripple frequency AC component with period of T\_rip\_low=2×20 ms+3×20 ms=100 ms. The low ripple frequency is F\_rip\_low=1/T\_rip\_low=10 Hz. Therefore, the output voltage ripple contains both low ripple frequency of 10 Hz and double line frequency ripple of 100 Hz.

- (6) Since the converter produces lower output voltage at low-gain mode operation than at high-gain mode operation, it draws less power from the AC source operating at low-gain mode than operating at high-gain mode for the same input AC voltage. That is, the power drawn from the AC source is different under different operating modes (high-gain mode and low-gain mode) when input AC voltage is same.

- (7) When the input AC voltage is same, the switching power converter may draw smaller AC sinusoidal current under low-gain mode operation, as compared with at high-gain mode operation. There may be varying AC sinusoidal current with varying peak values, corresponding to different operating modes.

- (8) To achieve a wide output voltage variation range, the values of Gain\_high and Gain\_low may be significantly different. For example, if Gain\_high is 2 times Gain\_low, the output voltage may be varied by 2:1 ratio with same control parameter value. If Gain\_high=1.1 times Gain\_low, the output voltage may be varied by only 1.1:1 ratio, which is less desirable.

- (9) In addition to high-gain and low-gain operation mode, a zero-gain operation mode may also be implemented. 55 Zero-gain operation mode may be defined as the power converter uses substantially no power from the AC source and therefore the output voltage is substantially zero when the converter operates at zero-gain mode under steady state operation. When the converter does not switch, the output voltage is typically zero. However, a boost converter is an exception. With a boost converter, the output voltage substantially equals the peak value of the AC voltage when the boost switch is not switching. Under normal operating condition, the output voltage of the boost converter is higher than the input voltage. Therefore, if the boost switch (e.g.,

14

MOSFET) is not switching, the boost diode will be reverse biased, and no energy will be transferred from input to output.

(10) With zero-gain mode the switching power converter may operate under three modes to achieve a particular output voltage level. In the following description, zerogain mode operation is not specifically emphasized since all the topologies can operate at zero-gain mode.

In some embodiments the time interval when the switching power converter operates at either high-gain mode or low-gain mode may be selected so that the output voltage is rising at high-gain mode operation and falling at low-gain mode operation, for example, such as shown in the simulation waveforms in FIG. 8 and FIG. 9.

5 1.2 Sub-Line Frequency Modulation Control Strategy

FIG. 6 is a block diagram of an AC-DC rectifier with two voltage gains: Gain\_high and Gain\_low, with power factor correction (PFC), according to one embodiment. With PFC operation, a relatively large capacitor (Co as shown in FIG. 6) is used at the load so that the output voltage is substantially a DC voltage with a small low frequency ripple. For example, Co=1,000 uF is used in the analysis and simulation, although other values may of course be used. The value of the ripple voltage (Vo\_rip\_pp) is small as compared with its DC value (Vo\_avg), normally less than about 20% of the DC value. The frequency of the ripple voltage is related to the line frequency.

In the following description of a control strategy, the below assumptions are made:

Assumption 1.1: An AC-DC rectifier with power factor correction has two operation modes: (1) high-gain operation mode and (2) low-gain operation mode.

Assumption 1.2: The voltage gain at high-gain operation mode (Gain\_high) is two times the voltage gain at low-gain operation mode (Gain\_low), Gain\_high=2\*Gain\_low. For example, Gain\_high=2 and Gain\_low=1. The voltage gain is defined as a ratio of the output DC voltage value to the input AC rms value, as shown in equations (8) and (9) below.

Assumption 1.3: The input AC voltage does not change.

40 In the analysis, as an example, Vac=200V rms and frequency of 50 Hz is used for illustration, and the converter operates at PFC mode.

Assumption 1.4: As an example, the maximum output voltage is 400V DC (200V rms\*2) and the DC load current is 5 A, the maximum output power is 2,000 W.

Assumption 1.5: As an example, for different output voltage levels, load current is always at 5A.

Assumption 1.6: Switching frequency (e.g., normally in the range of 100-200 kHz) is much higher than the line frequency (50 Hz or 60 Hz) and the switching frequency ripple is neglected.

Assumption 1.7: The value of the output capacitor is large so that the low frequency ripple voltage across the output capacitor (same as the output voltage) is much smaller than its average value (or DC value).

It is noted that Gain\_high is defined as the ratio of the output DC voltage (average voltage) to the rms value of the AC voltage when the AC-DC rectifier operates at high-gain mode. Gain\_low is defined as the ratio of the output DC voltage (average voltage) to the rms value of the AC voltage when the AC-DC rectifier operates at low-gain mode. Therefore:

(8)

where Vac is the rms value of the input AC line voltage.

FIG. 7A shows simulation results when converter operates at high-gain mode all the time. Under this condition, the output voltage (top) is 400V. The average value is 400V and the low frequency ripple is about 16V peak to peak. The second waveform (from top) is the AC input voltage. The third waveform (from top) is the input AC current. The bottom waveforms are input power, Pinput, and output power, Pout. The input power is a sinusoidal shape. The output power is almost a DC value with small ripple.

FIG. 7B shows simulation results when the converter operates at low-gain mode. At this condition, the output voltage (top) is 200V with low frequency ripple of about 16V peak to peak.

FIG. 8 shows simulation results under sub-line frequency 15 modulation when N high=5 and N low=2. Under this condition, the converter operates at high-gain mode for five line-cycles and operates at low-gain mode for two linecycles. With this control method, the average output voltage (top) is about 343V, and the peak-to-peak value of the low 20 frequency ripple is Vo\_rip\_pp=92V. The output power is 1,721 W. From time T1 (T1=about 2.1 second) to time T2 (T2=about 2.2 seconds), the converter operates at high-gain mode and the output voltage rises. The input current is high during this period. From time T2 to T3 (T3=about 2.24 25 seconds), the converter operates at low-gain mode and the output voltage decreases. The time interval from T1 to T3 is 140 ms, which equates to (N\_high+N\_low)\*T\_line=(5+2) \*20 ms=140 ms.

It is observed with sub-line frequency modulation, the 30 average output voltage is reduced from 400V to 343V. The converter operates alternatively between high-gain mode and low-gain mode. The operating conditions of these two modes are optimal with high efficiency.

It is also noted that during high-gain mode operation, the 35 input power is high (with peak value of 4,000 W). During low-gain mode operation, the input power is low (with peak value of 2,000 W).

Another observation is that with sub-line frequency modulation control, the output voltage does not reach steady 40 state under either high-gain operation mode or low-gain operation mode. For example, at the end of the high-gain operation, at T2 (FIG. 8), the output voltage continues to increase if high-gain mode operation continues. Similarly, at the end of low-gain mode operation, at T3 (FIG. 8), the 45 output voltage continues to decrease if low-gain mode continues. Since this is a low frequency change, or low frequency ripple, the low frequency ripple may be removed using another DC-DC converter as a second stage.

It is noted that the sub-line frequency modulation will 50 regulated based on the following relationship: change the DC value of the output voltage of a converter with power factor correction. It will not remove the low frequency ripple voltage of the converter. Another DC-DC converter will be needed to remove the low frequency ripple voltage to produce a pure DC voltage.

FIG. 9 shows simulation results of sub-line frequency modulation at N\_high=7 (high-gain mode operation for seven line cycles) and N\_low=1 (low-gain operation for one line cycle). In this case, Vo\_avg=375V, Vo\_rip\_pp=60V and output power is Pout=1,876 W.

FIG. 10 shows simulation results of sub-line frequency modulation at N\_high=2 (high-gain mode operation for two line cycles) and N\_low=2 (low-gain mode operation for two line cycles). In this case, Vo\_avg=300V, Vo\_rip\_pp=78V and output power is Pout=1,500 W.

FIG. 11 shows simulation results of sub-line frequency modulation at N\_high=2 (high-gain mode operation for two

line cycles) and N\_low=5 (low-gain mode operation for five line cycles). In this case, Vo\_avg=257V, Vo\_rip\_pp=112V and output power is Pout=1,302 W.

16

From the above analysis, it has been demonstrated that by changing the number of AC line cycles of high-gain mode operation (N\_high) and low-gain mode operation (N\_low), the output voltage of the AC-DC rectifier can be changed by sub-line cycle operation. The term "sub-line cycle" refers to the fact that the control period is an integer number times the 10 AC line period. In the cases shown in FIGS. 8 and 11, the control period is 7 times (N high+N low=7) the line period. In the case shown in FIG. 9, the control period is 8 times the line period. In the case shown in FIG. 10, the control period is 4 times the line period. Another low frequency ripple, which is lower than the line frequency, is generated.

1.3 Continuous Adjustment of Output Voltage DC Value

In the above analysis (1) the gain value of high-gain mode operation (Gain\_high) and low-gain mode operation (Gain\_ low) is fixed, and (2) the number of AC line cycles for high-gain mode operation (N\_high) and for low-gain mode operation (N low) are integer values. Therefore, the DC output voltage value will be a discrete value. Under these conditions the DC output voltage value cannot be adjusted continuously.

In a practical implementation the optimal operation, such as high efficiency mode operation, will be maintained over a limited range of gain values. For example, with an LLC converter, the high efficiency mode operation may be maintained for a voltage gain range of 1.8 to 2.2, or a variation of ±10%. Therefore, the DC value of the output voltage of the converter may be regulated accurately to a desired value by changing the actual gain of the converter.

For example, FIG. 12 shows simulation results when N\_high=5, N\_low=2, Gain\_high=2, and Gain\_low=1.04. In this case, the DC value of the output voltage is 345V, which is slightly higher than 342.7V when N\_high=5, N\_low=2, Gain\_high=2 and Gain\_low=1, as shown in FIG. 8.

Since the gain value of the AC to DC switching converter can be adjusted continuously, the DC value of the output voltage can also be regulated to any desired value. This may be achieved by, e.g., feedback control. In the case of PWM converter embodiments, the gain may be adjusted by changing the duty cycle. In the case of resonant converter embodiments, the gain may be adjusted by changing the switching frequency.

Similarly, the gain value under high-gain mode operation (Gain\_high) may also be adjusted to achieve accurate output voltage regulation. The details are not presented here.

Therefore, the output voltage of the converter may be

- (1) Larger N\_high value will increase the output voltage.

- (2) Larger N\_low value will decrease the output voltage.

- (3) Larger Gain\_high will increase the output voltage.

- (4) Larger Gain\_low will increase the output voltage.

- (5) Higher N\_high/N\_low ratio will increase the output voltage.

All four parameters, N\_high, N\_low, Gain\_high, and Gain low, may be used to control the output voltage. Examples of strategies to achieve desirable combinations are 60 outlined below.

- (1) To reduce the low frequency output voltage ripple, smaller N\_high and N\_low values may be used.

- (2) To maintain a selected operating condition, such as high efficiency, the parameters of the converter may be selected in such a way that the voltage gain variation is limited for either high-gain mode operation (such as from 1.8 to 2.2), or for low-gain mode operation (such

as from 0.9 to 1.1). A wide variation of the DC output voltage level may be achieved by sub-line frequency modulation operation.

As an example for point (1) above, an operation mode of N\_high=5 and N\_low=5 (mode A) will produce the same 5 DC value of the output voltage as an operation mode of N\_high=1 and N\_low=1 (mode B). With mode A, the period of low frequency ripple will be 10 times (5+5) the line period, which is T\_rip\_low=(5+5)×20 ms=200 ms for 50 Hz AC system. With mode B, the period of the low frequency ripple is 2 times (1+1) the line frequency, which is T\_rip\_low=(1+1)×20 ms=40 ms. Therefore, the output voltage ripple is smaller for mode B operation, which is desirable

With respect to point (2) above, it is generally observed that the wider the voltage gain required, the more design penalty will be imposed to the converter. Therefore, the converter will achieve worse performance. For example, consider two designs using an LLC converter. Design 20 LLC\_A requires voltage gain variation of 2 to 3, and design LLC\_B requires voltage gain variation of 2 to 2.2, while all other requirements are the same. Design LLC\_B will achieve better performance, such as higher efficiency, than design LLC\_A. Accordingly, design LLC\_B will be pre- 25 ferred.

Therefore, with sub-line frequency modulation technology, the converter operates at different gain modes and wide output voltage variation range can be achieved, while the gain variation for the converter itself is small.

#### 1.4 Sub-Double-Line Frequency Modulation

In order to reduce the low frequency output voltage ripple, the sub-line frequency modulation may be extended to sub-double-line frequency modulation. In this case, the high-gain mode operation and low-gain mode operation may 35 be decided based on half period of AC line cycles, such as 10 ms for 50 Hz system and 8.33 ms for 60 Hz system. For example, the converter operates alternatively between highgain mode for N\_half\_high half AC line cycles and low-gain mode for N\_half\_low half AC line cycles (where N\_half\_ 40 high and N\_half\_low are integers), and then the converter returns to high-gain operating mode again. For example, assuming 50 Hz AC line, the converter operates at high-gain mode for 3 half line cycle, or for 3×10 ms=30 ms, and then operates at low-gain mode for 2 half line cycles, or for 2×10 45 ms=20 ms.

A difference between sub-line frequency modulation and sub-double-line frequency modulation is the minimum time interval. With sub-double-line frequency modulation, the minimum interval is half the line period. For 50 Hz AC 50 system, the minimum interval is 10 ms. For 60 Hz AC system, the minimum interval is 8.33 ms.

FIG. 13 shows simulation results under the sub-double-line frequency modulation when N\_half\_high=5 and N\_half\_low=2. Under this condition, the converter operates at 55 high-gain mode for five (5) half line-cycles (5×10 ms=50 ms) and operates at low-gain mode for two (2) half line-cycles (2×10 ms=20 ms). With this control method, the average output voltage is about 342.7V, and the peak-to-peak value of the low frequency ripple is Vo\_rip\_pp=55V. 60 The output power is 1,717 W. From time T1 (T1=about 2.1 second) to time T2 (T2=about 2.15 second), the converter operates at high-gain mode and the output voltage rises. The input current is high during this period. From time T2 to T3 (T3=about 2.17 second), the converter operates at low-gain mode and the output voltage falls. The time interval from T1 to T3 is 70 ms, which equates to (N\_half\_high+N\_half\_low)

18

\*T\_half\_line=(5+2)\*10 ms=70 ms. T\_half\_line is the half line period. T\_half\_line=T\_line/2=10 ms.

The following may be observed by comparing the simulation results shown in FIG. 8 and FIG. 13:

- (1) The DC output voltage value is substantially the same. This is because the relative proportion of the high-gain mode operation and low-gain mode operation is the same.

- (2) The ripple voltage for FIG. 13 is 55V, (Vo\_rip\_pp=55V), while the ripple voltage for FIG. 8 is 92V (Vo\_rip\_pp=92V). The ripple is reduced by approximately one-half with sub-double-line frequency modulation.

- (3) The low frequency ripple period is 70 ms for sub-double-line frequency modulation (FIG. 13) and 140 ms for sub-line frequency modulation (FIG. 8).

FIG. **14** shows simulation results of sub-double-line frequency modulation at N\_half\_high=7 (high-gain mode operation for seven half line-cycles, 7×10 ms=70 ms) and N\_half\_low=1 (low-gain operation for one half line cycle, 1×10 ms=10 ms). In this case, Vo\_avg=375V, Vo\_rip\_pp=38V and output power is Pout=1,875 W.

FIG. 15 shows simulation results of sub-double-line frequency modulation at N\_half\_high=2 (high-gain mode operation for two half line-cycles, 2×10 ms=20 ms) and N\_half\_low=2 (low-gain mode operation for two half line-cycles, 2×10 ms=20 ms). In this case, Vo\_avg=300V, Vo\_rip\_pp=38V and output power is Pout=1,500 W.

FIG. 16 shows simulation results of sub-double-line frequency modulation at N\_half\_high=2 (high-gain mode operation for two half line-cycles, 2×10 ms=20 ms) and N\_half\_low=5 (low-gain mode operation for five half line-cycles, 5×10 ms=70 ms). In this case, Vo\_avg=257V, Vo\_rip\_pp=66V and output power is Pout=1,290 W.

Comparing the simulation results of FIGS. 8 and 13, FIGS. 9 and 14, FIGS. 10 and 15, and FIGS. 11 and 16, it can be observed that sub-double-line frequency modulation has features of the sub-line frequency modulation method, while achieving much smaller (almost reduced by half) low frequency ripple voltage. Therefore, sub-double-line frequency modulation method may be a preferred implementation method. In the rest of this description, only sub-double-line frequency modulation will be discussed.

It is also noted that in the above analysis, the switch-over between high-gain mode operation and low-gain mode operation happens at zero crossing point of the AC input voltage. However, the switch-over can happen at any AC input voltage. One benefit of switch-over at zero crossing point is that the transition will be smooth for high-gain mode operation and low-gain mode operation. Therefore, it may be advantageous to have switch-over at zero crossing point during steady state operation. During transient operation, it may be advantageous to have the switch-over when the instantaneous input voltage is not zero to improve the transient performance.

The consideration for selecting control parameters, such as N\_half\_high, N\_half\_low, Gain\_high, and Gain\_low, will be same for sub-double-line frequency modulation and for sub-line frequency modulation.

1.5 Extension to Output Voltage Lower than the Value Achieved by the Low-Gain Mode

The above analysis assumes a high-gain value of 2 and low-gain value of 1 and assumes the input voltage is 200V rms. Therefore, the steady state output voltage would be 400V (200V\*2) for high-gain mode operation and 200V (200V\*1) for low-gain mode operation. With the sub-line frequency modulation and sub-double-line frequency modu-

lation, the output voltage may be regulated between 200V and 400V, or between the steady state output voltage values of the high-gain mode operation and low-gain mode operation.

If the desired output voltage is below 200V, such as 150V, a zero-gain operation mode may be introduced and the converter operates between low-gain mode and zero-gain mode. Under zero-gain mode, the steady state output voltage will be zero.

In the above example, if the output voltage of the converter is required to be regulated at about 150V, while the output of the converter is 200V at low-gain operation, then one possible operation is as following:

- (1) The converter operates at low-gain mode for N\_low line cycles, or N\_half\_low half-line cycles;

- The converter then operates at zero-gain mode for N\_zero line cycles, or N\_half\_zero half-line cycles;

- (3) The converter repeats the above operations.

N\_zero is the number of AC line cycles when the converter operates at zero-gain operation mode. When there is no energy transfer from input to output, the output voltage will be zero in steady state. N\_half\_zero is the number of AC half-line cycles when the AC-DC rectifier operates at zero-gain mode.

In the above example and control strategy, the output voltage of the AC-DC rectifier may be regulated at about 150V. The following are noted:

- (1) Smaller value of N\_low and N\_zero are used to reduce the low frequency ripple of the output voltage.

- (2) When different N\_low and N\_zero are used, the output voltage may be regulated between 0V and 200V.

- (3) Sub-double-line frequency modulation may also be used. In this case, the converter operates at low-gain mode for N\_half\_low half-line cycles and N\_half\_zero 35 half-line cycles.

- (4) The number of N\_low, N\_zero and N\_half\_low, N\_half\_zero may be small enough so that the output voltage of the AC-DC rectifier is a DC value (Vo\_avg) with a low frequency ripple (Vo\_rip\_pp). For example, 40 the values may be selected to maintain Vo\_rip\_pp less than 10% to 50% of the Vo\_avg.

FIG. 17 shows simulation results when Vac=200V, N\_hal-f\_low=6, N\_half\_zero=2. With this operating condition, the output voltage is Vo\_avg=150V. The peak-to-peak value of 45 the low frequency ripple is 55V.

#### 2 Control Strategy for Input Voltage Variation

The above analysis shows that the output voltage may be 50 changed by Variable Gain Modulation method (sub-line frequency modulation). This section shows that the output voltage may be maintained at approximately the same value when the input voltage changes over wide range.

The following assumptions are made in the below analysis:

Assumption 2.1: A converter with power factor correction has two operation modes: (1) high-gain operation mode and (2) low-gain operation mode.

Assumption 2.2: The voltage gain at high-gain operation mode (Gain\_high) is two times the voltage gain at low-gain operation mode (Gain\_low), Gain\_high=2\*Gain\_low, for example, it is assumed that Gain\_high=2 and Gain\_low=1. It is noted that the gain is defined as Vo\_avg/Vac.

Assumption 2.3: The input AC voltage will change between Vac1=100 Vrms and Vac2=200 Vrms, a 2:1 change

20

ratio. In the analysis, an AC line frequency of 50 Hz is used for illustration purposes. The AC-DC rectifier operates at PFC mode

Assumption 2.4: The output voltage is regulated at 150V DC and the DC load current is 5 A over the above input voltage variation (between 100 Vrms and 200 Vrms). Therefore, the output power is 750 W. The load resistor is 300.

Assumption 2.5: For different input voltage levels, load current is always 5 A.

Assumption 2.6: Switching frequency (normally in the range of 100-500 kHz) is much higher than the line frequency (50 Hz or 60 Hz) and the switching frequency ripple is neglected.

Assumption 2.7: Sub-Double-Line frequency modulation is used. The operation for Sub-Line frequency modulation will be same.

As an example, the average value of the output voltage is regulated at 150V when the input AC voltage changes from 100V to 200V.

When the input AC voltage is 100V, FIG. 18 the simulated waveforms show that when the converter operates at highgain mode (Gain\_high=2) for 4 half line cycles (N\_half\_high=4, or 4\*10 ms=40 ms) followed by operating at low-gain mode (Gain\_low=1) for the next 4 half line cycles (N\_half\_low=4, or 4\*10 ms=40 ms), the output voltage may be regulated at 150V. If the converter operates at high-gain mode for long time, such as 10 to 50 line cycles, the output voltage will be at 2×100=200V. On the other hand, if the converter operates at low-gain mode for long time, the output voltage will be 1×100=100V. Therefore, by operating between high-gain mode and low-gain mode, the output voltage can be regulated at 150V.

When the input AC voltage changes to 120V, the steady-state value of the output voltage regulation range is 120V (at low-gain mode operation) and 120V×2=240V (at high-gain mode operation). FIG. 19 shows simulated operation waveforms. In this case, the converter operates at high-gain mode for 2 half line cycles, N\_half\_high=2, and operates at low-gain mode for 6 half line cycles, N\_half\_low=6. The average value of the output voltage is regulated at 150V.

When the input AC voltage is 150V, then the converter operates at low-gain mode all the time and the average value of the output voltage will always be 150V.

When the input AC voltage is 200V, even if the converter operates at low-gain mode, Gain\_low=1, the steady-state value of the output voltage will still be 200V, which is higher than the required 150V. Therefore, the converter should operate at low-gain mode and zero-gain mode. FIG. 20 shows simulation results when the converter operates at low-gain mode for 6 half-line cycles (N\_half\_low=6) and operates at zero-gain mode for 2 half-line cycles (N\_half\_zero=2). Then the output voltage may be regulated at 150V.

It is noted that the converter may also operate at high-gain mode and zero-gain mode to produce 150V but this will increase the voltage and/or current of the converter.

55 In the above example with the parameters: Vin\_min=100V, Vin\_max=200V, and Gain\_low=1 and Gain\_high=2, the max possible output voltage at Vin\_min is Vin\_min\*Gain\_high=200V. If higher output voltage is required, larger Gain\_high may be implemented. The output voltage may then be regulated to any value between 200V and 0V.

## 3 Combination of Input Voltage Variation and Output Voltage Variation

The embodiments described above used variable gain modulation over sub-line frequency and sub-double-line

frequency for an converter with power factor reaction to achieve (1) wide output voltage variation range when the input AC voltage is fixed; (2) fixed output voltage when the input AC voltage varies over a wide range. There are three operation modes: (1) high-gain mode, (2) low-gain mode, <sub>5</sub> and (3) zero-gain mode.

It was demonstrated above that by adjusting the gain value of either high-gain mode or low-gain mode, or both, the output voltage may be regulated continuously.

In a practical implementation, the input AC voltage could have a wide variation range and the output voltage could also have a wide regulation range. A control method according to embodiments described herein can also achieve this objective.

The following assumptions are made to illustrate a detailed implementation, as one example:

Assumption 3.1: Sub-double-line frequency modulation is used since it will produce lower output voltage ripple.

22

In case 1.4, a voltage gain value of 0.97 at low-gain mode operation is needed to fine tune the output voltage to 100V.

Comparing case 1.3 and case 1.6, when input voltage is increased from 150V to 155V, a voltage gain value of 0.99 at low-gain mode operation is used to fine tune the output voltage to 100V. N\_half\_low and N\_zero value remains the unchanged.

In all cases, Vo\_avg=100V and Vin=100V to 200V, only low-gain mode operation and zero-gain mode operation are needed. High-gain mode operation is not activated. NO means No Operation for that operation mode.

For case 1.4, the converter operates at low-gain mode for 4 half line cycles (N\_half\_low=4), operates at zerogain mode for 3 half line cycles (N\_half\_zero=3), and the actual gain value at low-gain mode is 0.97. Then the output DC voltage is 100.1V. The converter does not operate at high-gain mode.

TABLE 2

| Operating conditions for required output voltage Vo_avg = 200 V |                  |            |             |             |          |           |         |

|-----------------------------------------------------------------|------------------|------------|-------------|-------------|----------|-----------|---------|

| Case #                                                          | Vin              | N_half_low | N_half_high | N_half_zero | Gain_low | Gain_high | Vo_avg  |

| Case 2.1                                                        | 100 V            | NO         | Continuous  | NO          | NO       | 2         | 200.0 V |

| Case 2.2                                                        | 120 V            | 2          | 4           | NO          | 1        | 2         | 200.2 V |

| Case 2.3                                                        | 150 V            | 4          | 2           | NO          | 1        | 2         | 200.2 V |

| Case 2.4                                                        | $180~\mathrm{V}$ | 9          | 1           | NO          | 1        | 2         | 200.0 V |

| Case 2.5                                                        | 200 V            | Continuous | NO          | NO          | 1        | NO        | 200.0 V |

| Case 2.6                                                        | 155 V            | 4          | 2           | NO          | 1        | 1.88      | 200.6 V |

Assumption 3.2: Input AC voltage variation range may be from  $100\mathrm{V}$  rms to  $200\mathrm{V}$  rms with line frequency of 50 Hz.

Assumption 3.3: Output voltage may be regulated at any value between  $100 \mathrm{V} \ \mathrm{DC}$  to  $200 \mathrm{V} \ \mathrm{DC}$ .

Assumption 3.4: The load current is 5 A under all output voltages. The analysis result will be the same for different load currents.

Assumption 3.5: The high-gain value is Gain\_high=2 and it may be changed from 1.8 to 2.2 (for a  $\pm 10\%$  change) while maintaining high performance operation.

Assumption 3.6: The low-gain value is Gain\_low=1 and it may be changed from 0.9 to 1.1 (for a  $\pm 10\%$  change) while maintaining high performance operation.

The following tables provide a summary of the operating conditions to achieve the above design requirements, according to simulations.

Notes:

In the above simulation, an error of less than 1.0V (0.5% of 200V) is assumed. When the output voltage is between 199V and 201V, it is considered that 200V is achieved.

Between case 2.3 and case 2.6, the N\_half\_low and N\_half\_high is the same for both conditions, Gain\_high is changed to 1.88 for 155V input so that the output voltage may be regulated to 200V.

When input voltage is 100V, the rectifier operates at high-gain mode continuously. When the input is between 100V and 110V, the rectifier operates at high-gain mode operation continuously and the output voltage may be regulated to 200V by changing the gain of the rectifier (from 1.8 to 2).

When input voltage is 120V, the rectifier operates at low-gain mode for 2 half-line cycles and at high-gain mode for 4 half-line cycles.

TABLE 1

| Operating conditions for required output voltage Vo_avg = 100 V |       |            |             |             |          |           |                    |

|-----------------------------------------------------------------|-------|------------|-------------|-------------|----------|-----------|--------------------|

| Case #                                                          | Vin   | N_half_low | N_half_high | N_half_zero | Gain_low | Gain_high | Vo_avg             |

| Case 1.1                                                        | 100 V | Continuous | NO          | NO          | 1        | NO        | 100.0 V            |

| Case 1.2                                                        | 120 V | 2          | NO          | 10          | 1        | NO        | 100.5 V            |

| Case 1.3                                                        | 150 V | 2          | NO          | 4           | 1        | NO        | 100.5 V            |

| Case 1.4                                                        | 180 V | 4          | NO          | 3           | 0.97     | NO        | $100.1~\mathrm{V}$ |