# A Control Strategy and Design Method for Interleaved LLC Converters Operating at Variable Switching Frequency

Zhiyuan Hu, Student Member, IEEE, Yajie Qiu, Student Member, IEEE, Yan-Fei Liu, Fellow, IEEE, and Paresh C. Sen, Life Fellow, IEEE

*Abstract*—LLC converters face challenges in high-current applications, where the high conduction loss limits the maximum load capacity and reduces efficiency. Interleaving technique can be used to solve this problem, but the component tolerances of the resonant tanks will cause severe load sharing problem. The SCC–LLC converter was proposed to solve the load sharing problem. However, due to its constant switching frequency operation, it has some limitations over complete line and load variation compared to conventional LLC converters. In this paper, a new control strategy is proposed for the SCC–LLC converter, which enables variable switching frequency operation; thus, it provides uncompromised performance while achieving interleaved operation. Analyses and a design method are provided, and a 600-W two-phase interleaved SCC–LLC prototype is built to verify the feasibility.

*Index Terms*—Interleaving, load sharing, resonant power conversion, switched-mode power supply.

## I. INTRODUCTION

**T** ODAY'S power converters are required to deliver more power and achieve high efficiency in a wide load range. These requirements are sometimes contradictive, because when the current is high, the conduction loss is dominant, then the efficiency is likely to suffer. To solve this problem, interleaving and phase-shedding techniques have been developed, and they have the following advantages: 1) in heavy load condition, multiple phases can split the total current, thus mitigate the I<sup>2</sup>R loss and other associated losses; 2) in light load condition, unneeded phases can be shut down, thus the light-load efficiency can be improved; and 3) output ripple current are cancelled by the interleaved phases, thus the output capacitor size can be smaller.

The LLC resonant topology [1]–[4] has been popularly adopted in flat panel TVs [5], laptop adaptors [6], [7], LED lighting [8], [9], computer [10], battery charger [11], renewable energy [12]–[15], transportation [16]–[18], and so on. The below-resonance region of the LLC converters has advantages

Manuscript received August 4, 2013; revised October 31, 2013; accepted January 2, 2014. Date of current version March 26, 2014. Recommended for publication by Associate Editor R.-L. Lin.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2014.2300165

such as zero-voltage switching (ZVS) for main switches, zerocurrent switching (ZCS) for output rectifiers, narrow frequency variation range, etc., resulting in high efficiency. However, interleaving LLC converters has a difficulty: when interleaved, all the LLC stages must operate at the same switching frequency; whereas due to the components' tolerances, individual LLC stages may have different resonant frequencies, thus the output currents will be different. Simulation results in Section IV will show that the normal component tolerances can cause severe load sharing problem.

Previous studies on interleaved LLC converters all have limitations. The interleaved LLC converters in [19]–[22] did not consider the load sharing problem caused by the component tolerances. The load sharing method in [23] needs an additional power stage to regulate the output voltage and does not work for more than two phases interleaved. The structure in [24] divides down the input voltage by the number of phases; therefore, the load capacity is still limited and it has difficulties with phase shedding. The topology in [25] also has difficulties with phase shedding. The variable inductor method in [26] requires a controlled dc current source to saturate the inductor, thus is less efficient.

The switch-controlled capacitor (SCC)–LLC converter was proposed in [27]. It uses an SCC [28] in each LLC power stage to control the resonant frequency. Therefore, output voltage regulation is achieved with constant switching frequency operation, which provides a simple solution for interleaving, load sharing, and phase shedding. However, the constant switching frequency operation also imposes some limitations over complete line and load variation compared to conventional LLC converters with switching frequency control.

In this paper, a new control strategy is proposed for the SCC– LLC converter. It achieves variable switching frequency operation and interleaving at the same time. Section II reviews the constant switching frequency SCC–LLC converter; Section III proposes the new control strategy; Section IV provides analyses and a design method of the new control strategy; Section V shows the experimental results; and Section VI is the conclusion.

## II. REVIEW OF CONSTANT SWITCHING FREQUENCY SCC-LLC CONVERTER

The concept of SCC was proposed in [28] and has been applied in various applications to obtain constant switching frequency operation [29]–[34]. It includes the full-wave SCC and

0885-8993 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

The authors are with the Department of Electrical and Computer Engineering, Queen's University, Kingston, ON K7L 2W1 Canada (e-mail: zhiyuan.hu@ queensu.ca; yajie.giu@queensu.ca; yanfei.liu@queensu.ca; senp@queensu.ca).

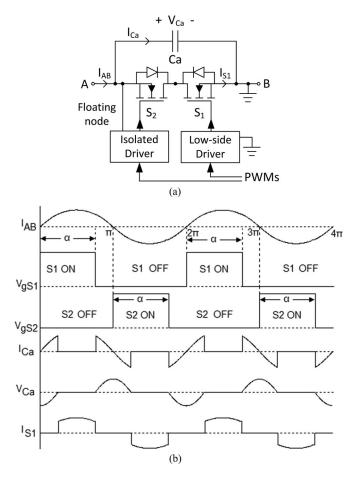

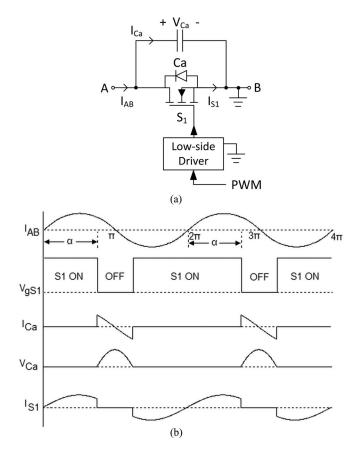

Fig. 1. Structure and waveforms of full-wave SCC. (a) Structure of full-wave SCC. (b) Waveforms of full-wave SCC.

the half-wave SCC. Both structures consist of a capacitor in parallel with one or two switches. When the switches are turned ON, the current bypasses the capacitor, thus the circuit behaves noncapacitive. When the switches are turned OFF, the current flows through the capacitor, thus the circuit behaves capacitive. The equivalent capacitance of SCC,  $C_{\rm SC}$ , can be modulated by the turn-off angle of the switches.

Fig. 1 shows the structure and waveforms of a full-wave SCC. The equivalent capacitance of the full-wave SCC,  $C_{\rm SC,FW}$ , is modulated by the angle  $\alpha$  ( $\pi/2 < \alpha < \pi$ ), given in (1) [28]. The angle  $\alpha$  is synchronized at the zero-crossing points of the resonant current

$$C_{\rm SC,FW} = \frac{C_a}{2 - (2\alpha - \sin 2\alpha)/\pi}.$$

(1)

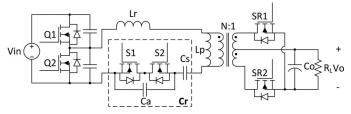

The previously proposed constant switching frequency SCC– LLC converter [27] is illustrated in Fig. 2. A full-wave SCC is connected in series with the resonant tank in order to modulate the resonant capacitance. The equivalent resonant capacitance,  $C_r$ , is derived as follows:

$$C_r = \frac{C_{\rm SC}C_s}{C_{\rm SC} + C_s}.$$

(2)

The operation principle of the constant switching frequency SCC–LLC converter is described as follows.

Fig. 2. Topology of the constant switching frequency SCC-LLC converter.

The switching frequency is constant. The SCC's turn-off angle  $\alpha$  controls the equivalent resonant capacitance  $C_r$ , which in turn controls the resonant frequency, and thus, the output voltage gain of the SCC–LLC converter. In an interleaved multiphase SCC–LLC converter, all the phases are operating at the same constant switching frequency with shifted phase angles to facilitate the ripple cancellation. Each phase uses an SCC to regulate the output voltage and to achieve load sharing. For example, when the controller detects that one phase is providing more output current than other phases, it slightly increases the control angle  $\alpha$  of the corresponding phase, which increases the resonant capacitance  $C_r$  and lowers the resonant frequency, and thus reduces the output current until it reaches the balanced point. Different phases may use different  $\alpha$  angles to achieve load sharing because the component tolerances are usually different.

The aforementioned constant switching frequency SCC–LLC converter solves the load sharing problem for the interleaved LLC topology, and enables this highly efficient topology to be applied in high-current applications. However, as disclosed in [27], the constant switching frequency SCC–LLC converter exhibits different characteristics than conventional LLC converters, because it uses resonant frequency modulation (FrM) instead of switching frequency modulation (FsM). The differences of the two modulation methods are discussed as follows.

The voltage gain expression of an LLC resonant tank is derived in (3) using the fundamental harmonic approximation (FHA) method. The definitions are in (4) for quick reference. M is the gain of the resonant tank, where the factor 2 is due to the half-bridge configuration. N is the transformer turns ratio.  $L_p$  is the parallel inductance. K is the inductance ratio.  $R_L$  is the load resistance.  $\omega_s$  is the switching frequency in radians  $\omega_r$  is the resonant frequency in radians

$$M = \frac{K}{\sqrt{\left[\left(\frac{\omega_r}{\omega_s}\right)^2 - K - 1\right]^2 + \frac{\pi^4 \omega_s^2 L_p^2}{64N^4 R_L^2} \left[\left(\frac{\omega_r}{\omega_s}\right)^2 - 1\right]^2}}$$

$$M = \frac{NV_o}{V_c/2}, N = \frac{N_p}{N}, K = \frac{L_p}{L}, \omega_s = 2\pi f_s, \omega_r = \frac{1}{\sqrt{L_cC}}.$$

(3)

$$M = \frac{1}{V_{\rm in}/2}, \ N = \frac{1}{N_s}, \ K = \frac{1}{L_r}, \ \omega_s = 2\pi J_s, \ \omega_r = \frac{1}{\sqrt{L_r C_r}}.$$

(4)

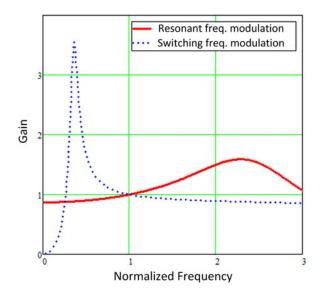

For a given set of values of  $L_p$ , K,  $R_L$ , and N, the gain curves resulted from FrM and FsM are plotted using (3), respectively, shown in Fig. 3. When plot the FrM curve,  $\omega_s$  is fixed and  $\omega_r$  is variable; the normalized frequency is defined as  $\omega_r/\omega_s$ . When

Fig. 3. Comparison of FsM and FrM.

plot the FsM curve,  $\omega_r$  is fixed and  $\omega_s$  is variable; the normalized frequency is defined as  $\omega_s/\omega_r$ . It is evident that the FsM provides a higher peak gain within a narrower frequency variation range than the FrM does. This phenomenon can be understood from the impedance point of view: the FsM modulates the impedance of all the resonant components, whereas the FrM only modulates the impedance of the resonant capacitance, thus is less effective.

The aforementioned analysis reveals that the previously proposed constant switching frequency SCC–LLC converter makes compromises in terms of peak gain range and normalized frequency variation range compared to conventional LLC converters. In order to take full advantage of the LLC topology, FsM is preferred.

In addition, Fig. 1 shows that, the full-wave SCC uses two MOSFETs and requires isolated driving. This increases the circuit complexity and the conduction loss. Half-wave SCC is more desirable if it can be used.

## III. PROPOSED VARIABLE SWITCHING FREQUENCY CONTROL STRATEGY

## A. Variable Switching Frequency SCC-LLC Converter

It is noted that the interleaving operation only requires that the switching frequency of all the interleaved phases be the same, yet the switching frequency of all the phases can change together in different operating conditions. It is also noticed that the FsM is more effective than the FrM. Therefore, a new control strategy is proposed as follows:

- 1) All the interleaved SCC–LLC phases operate at the same but variable switching frequency. The output voltage is controlled by the switching frequency.

- 2) The gate driving signals of all phases are interleaved so that the output current of all phases is interleaved for ripple cancellation.

- The load sharing among different phases is achieved by changing the equivalent resonant capacitance using the SCC technology.

In this way, the peak gain range and the frequency variation range of the SCC–LLC converter are the same as conventional LLC converters. The ZVS condition of the half-bridge switches is also the same as conventional LLC converters. The required capacitance variation range for the SCC is much smaller because it is only responsible for compensating the component tolerances to achieve load sharing; therefore, half-wave SCC can be used.

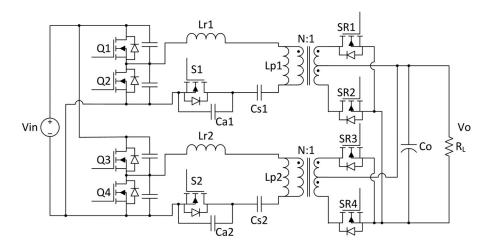

The new control strategy can be applied in the topology in Fig. 2, but the full-wave SCC is unnecessary and can be reduced to a half-wave SCC. The modified topology suitable for the new control strategy is shown in Fig. 4.

### B. Comparison of Full-Wave SCC and Half-Wave SCC

Fig. 5 shows the structure and waveforms of a half-wave SCC. The control scheme is similar to that of the full-wave SCC, except that there is only one MOSFET, and the control angle  $\alpha$  is from 0 to  $\pi$ .

In order to reduce the power loss on the MOSFET's body diode, in this paper, the SCC MOSFET is turned ON as soon as the  $C_a$  voltage is discharged to zero. From the  $C_a$  voltage zerocrossing point to the resonant current zero-crossing point, the MOSFET acts like a synchronous rectifier. It has no impact on the equivalent capacitance modulation.

The equivalent capacitance of the half-wave SCC,  $C_{SC,HW}$ , is given in [33], and is rewritten in (5) after rearrangement

$$C_{\rm SC,HW} = \frac{2C_a}{2 - (2\alpha - \sin 2\alpha)/\pi}.$$

(5)

The comparison of the full-wave SCC and the half-wave SCC includes the following aspects:

- 1) *Cost.* The half-wave SCC has only one MOSFET and does not require isolated driving; therefore, its cost is lower than that of the full-wave SCC.

- 2) Power loss. The half-wave SCC has only one MOSFET; therefore, its conduction loss and gate driving loss are lower than that of the full-wave SCC. Both the full-wave and the half-wave SCCs have ZVS conditions at turn-on and turn-off; therefore, there is no switching loss.

- 3) Capacitance regulation capacity. The control angle  $\alpha$  of a full-wave SCC is from  $\pi/2$  to  $\pi$ . Substituting  $\alpha$  into (1) gives that the resultant capacitance regulation range is from  $C_a$  to infinity. Likewise, the control angle  $\alpha$  of a half-wave SCC is from 0 to  $\pi$ . Substituting  $\alpha$  into (5) gives that the resultant capacitance regulation range is also from  $C_a$  to infinity. Therefore, the half-wave SCC and the fullwave SCC have the same capacitance regulation capacity. This analysis result can be understood by considering the two extreme cases: when the control angle  $\alpha$  is minimum  $(\pi/2 \text{ for full-wave SCC}, \text{ and } 0 \text{ for half-wave SCC}), the$ capacitor  $C_a$  is always connected in the resonant circuit, therefore its equivalent capacitance is  $C_a$ ; when the control angle  $\alpha$  is maximum ( $\pi$  for both full-wave and half-wave SCCs), the capacitor  $C_a$  is always shorted by the MOSFET, therefore its equivalent capacitance is infinite.

- 4) *Symmetry*. The full-wave SCC can perform modulation when the resonant current is in both directions; therefore,

Fig. 4. Modified SCC-LLC converter suitable for the variable switching frequency control strategy.

Fig. 5. Structure and waveforms of half-wave SCC. (a) Structure of half-wave SCC. (b) Waveforms of half-wave SCC.

the SCC voltage waveform is symmetrical in both halfcycles. This is favorable for LLC converter because the output current in both half-cycles will be the same. The half-wave SCC can perform modulation only in one direction; therefore, the SCC's waveforms will be asymmetrical, causing the output current of the two half-cycles nonidentical. This effect can be observed in Fig. 16. In order to restrict the asymmetrical effect within an acceptable level, the SCC voltage amplitude should be kept low, which means the capacitance variation range should be small. As a result, half-wave SCC is not desirable in constant switching frequency SCC–LLC converters, because the resonant capacitance needs to vary significantly in different operating conditions. However, half-wave SCC is suitable in variable switching frequency SCC–LLC converters, because the resonant capacitance only needs to vary by a small amount to compensate the component tolerances.

To sum up aforementioned analyses, the half-wave SCC has lower cost, lower power loss, the same capacitance regulation capacity, but asymmetrical waveforms compared to the fullwave SCC. Because the proposed control strategy only requires a small capacitance variation range for the SCC, the asymmetrical effect can be managed within an acceptable level. Therefore, the half-wave SCC is the best tradeoff between the cost and the performance in the proposed control strategy.

#### IV. ANALYSIS AND DESIGN METHOD

The proposed control strategy uses the switching frequency to regulate the output voltage; therefore, the design procedure is the same as in conventional LLC converters, which is available in many literatures [4], [35]–[38]. The only unknown parameter is the SCC capacitor value  $C_a$ . This section studies the load sharing characteristics of multiphase LLC converters, and then provides a design method to select the value of  $C_a$  according to component tolerance values.

## A. Load Sharing Characteristics

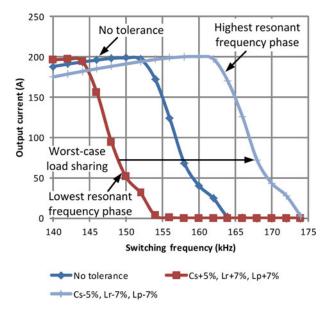

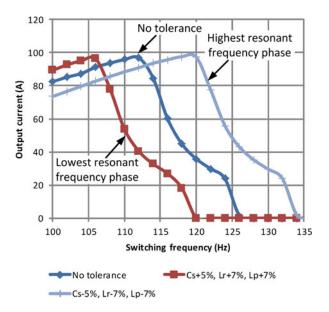

Due to components' tolerances, the resonant frequencies of interleaved LLC stages are slightly different from each other, resulting in different output-current-versus-switching-frequency curves. A set of such curves are obtained from simulation and plotted in Fig. 6. In this example,  $\pm 7\%$  tolerances are assumed for inductors, and  $\pm 5\%$  tolerances are assumed for capacitors. The specification is:  $V_{in} = 300 \text{ V}-400 \text{ V}$ ,  $V_o = 12 \text{ V}$ . Reasonable power train parameters are used: transformer turns ratio is 20:1; nominal component values of  $C_s$ ,  $L_r$ , and  $L_p$  are 40 nF, 12  $\mu$ H, and 86  $\mu$ H, respectively. The peak output current

Fig. 6. Output current versus switching frequency curves at different tolerances. Input voltage is 400 V. Output voltage is 12 V. Transformer turns ratio is 20:1.

obtained by simulation are the theoretical maximum capacity of such a resonant tank.

In Fig. 6, the rightmost curve represents the relation between output current and switching frequency when the resonant components are at their minimum tolerance values. The leftmost curve represents the relation between the output current and the switching frequency when the resonant components are at their maximum tolerance values. The middle curve represents the relation between output current and switching frequency with nominal resonant component values. This plot demonstrates that when two LLC converters are connected in parallel, in the worst case, no current sharing can be achieved. For example, at 170 kHz switching frequency, the output current of the aforementioned two phases are 50 and 0 A, respectively.

Fig. 8. Output current versus switching frequency curves at different tolerances. Input voltage is 300 V. Output voltage is 12 V. Transformer turns ratio is 20:1.

Fig. 9. Output current versus switching frequency curves after compensation. Input voltage is 300 V. Output voltage is 12 V. Transformer turns ratio is 20:1.

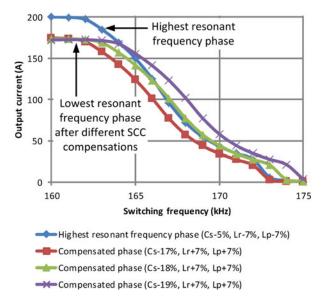

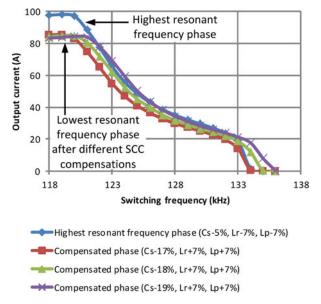

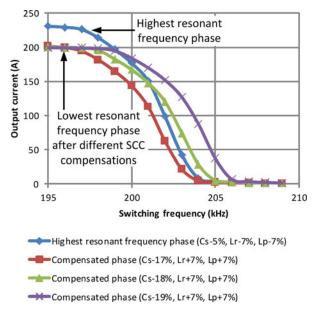

In order to achieve load sharing, SCC can be used to reduce the equivalent resonant capacitance of the lower output current phase, so that its output current will increase and match the higher output-current phase. Note that the SCC can only increase the resonant frequency, but not decrease; therefore, the highest resonant frequency phase in an interleaved SCC–LLC converter automatically becomes the reference phase. All the lower resonant frequency phases must be compensated by the SCC and match to the reference phase. The worst case for load sharing is to have these two extreme tolerance cases in the same interleaved SCC–LLC converter. In this scenario, the leftmost curve must be moved toward the rightmost curve until the two curves are matched. The compensation results are shown in Fig. 7.

Fig. 10. Output current versus switching frequency curves at different tolerances. Input voltage is 400 V. Output voltage is 12 V. Transformer turns ratio is 18:1.

Fig. 7 reveals that, from no load to heavy load, the required reduction of  $C_s$  to achieve load sharing is almost invariant. In this example, across the entire load range, 17% reduction of  $C_s$  always results in lower output current than the highest resonant frequency phase; 18% reduction of  $C_s$  results in the closest match of the output currents; and 19% reduction of  $C_s$  provides the best match at heavy load. Therefore, in this example, the worst case for SCC design is to achieve 19% reduction of the ideal  $C_s$  value.

Above simulation studies are repeated for 300 V input condition and 18:1 turns ratio, respectively. The simulation results are shown in Figs. 8–11. They show that with the same component tolerance values, the required resonant capacitance to achieve load sharing are both 19% reduction from  $C_s$  for either 300 V input condition or 18:1 turns ratio, identical to the case studied in Figs. 6 and 7. Therefore, the worst case of SCC design is only affected by the component tolerances, and does not change with input condition and turns ratio.

The aforementioned case studies illustrated the characteristics of load sharing by varying the resonant capacitance. A design method is developed in the next section.

### B. Design of Resonant Capacitance Variation Range

The expression of output current can be obtained from (3), and is shown in (6), at the bottom of the page.

Fig. 11. Output current versus switching frequency curves after compensation. Input voltage is 400 V. Output voltage is 12 V. Transformer turns ratio is 18:1.

Coefficients a, b, and c are defined as the ratios of the actual and ideal component values of  $L_p, L_r$ , and  $C_s$ , respectively, shown in (7), where the subscript 0 stands for ideal values without tolerances

$$a = \frac{L_p}{L_{p0}}, b = \frac{L_r}{L_{r0}}, c = \frac{C_s}{C_{s0}}.$$

(7)

Then the inductance ratio becomes

$$K_0 = \frac{L_{p0}}{L_{r0}}, \text{ and } K = \frac{L_p}{L_r} = \frac{aL_{p0}}{bL_{r0}} = \frac{a}{b}K_0.$$

(8)

And the resonant frequency and switching frequency become

$$\omega_{r0} = \frac{1}{\sqrt{L_{r0}C_{s0}}}, \text{ and } \omega_r = \frac{1}{\sqrt{L_rC_s}} = \frac{1}{\sqrt{bL_{r0} \cdot cC_{s0}}}$$

$$= \frac{1}{\sqrt{bc}}\omega_{r0} \tag{9}$$

$$\omega_s = \omega_n \cdot \omega_{r0} \tag{10}$$

where  $\omega_n$  is the switching frequency normalized at the ideal resonant frequency  $\omega_{r0}$ .

Substitute (8), (9), and (10) into (6), then  $I_o$  can be expressed as a function of  $\omega_n$ , a, b, and c, shown in (11), at the bottom of the page. Equation (11) shows that the output current of a

$$I_o = \frac{8V_o N^2 \sqrt{2\omega_r^2 K \omega_s^2 M^2 + 2\omega_r^2 \omega_s^2 M^2 - \omega_r^4 M^2 - \omega_s^4 M^2 - K^2 \omega_s^4 M^2 - 2K \omega_s^4 M^2 + K^2 \omega_s^4}{\pi^2 (\omega_r + \omega_s) (\omega_r - \omega_s) \omega_s L_p M}$$

(6)

$$I_{o}(\omega_{n},a,b,c) = \frac{8V_{o}N^{2}\sqrt{2aK_{0}\omega_{n}^{2}M^{2}c - M^{2} - \omega_{n}^{4}M^{2}b^{2}c^{2} + 2\omega_{n}^{2}M^{2}bc - a^{2}K_{0}^{2}\omega_{n}^{4}M^{2}c^{2} - 2aK_{0}\omega_{n}^{4}M^{2}bc^{2} + a^{2}K_{0}^{2}\omega_{n}^{4}c^{2}}{\pi^{2}\omega_{r0}\omega_{n}aL_{p0}M\left(1 - \omega_{n}^{2}bc\right)}$$

(11)

given LLC stage is determined by the switching frequency and the component tolerances.

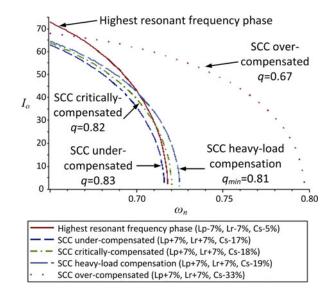

With a good SCC design, after compensating the tolerance of resonant components, the output current of the highest resonant frequency phase and the lowest resonant frequency phase should be the same. Equation (12) can describe such a relation. The lefthand side of (12) is the output current of the highest resonant frequency phase; the right-hand side of (12) is the output current of the lowest resonant frequency phase after SCC compensation. The coefficient q is the ratio of the required equivalent resonant capacitance,  $C_r$ , and the ideal series capacitor value,  $C_{s0}$ . As shown in Fig. 7, the required q value slightly varies in different load conditions. The minimum value of  $q, q_{\min}$ , is the worst case scenario for the SCC design, which happens when the corresponding SCC control angle  $\alpha$  is minimum.

$$I_o(\omega_n, a_{\min}, b_{\min}, c_{\min}) = I_o(\omega_n, a_{\max}, b_{\max}, q)$$

(12)

where  $q = \frac{C_r}{C_{s0}}$  due to SCC modulation.

The expression of q can be derived from (11) and (12). Then its values can be calculated at different switching frequency points. The minimum value of q can be identified accordingly. However, this approach could result in severe overdesign. This is because the equation is based on FHA, which assumes sinusoidal waveforms; but when the LLC converter operates near the peak gain point, the switching frequency is far below the resonant frequency, thus the waveforms are no longer sinusoidal, and consequently, large errors are resulted [37], [39], [40]. Because the  $q_{\min}$  always happens at the peak gain point, the FHA approach is less than ideal.

Nevertheless, the FHA-based equation provides good accuracy at a lower gain region. Therefore, the q value at light load condition can be accurately estimated using the FHA-based equations. Also, according to the observations made in the previous section, the required resonant capacitance to achieve load sharing only varies a little from light load to heavy load. Therefore, after the light-load q value is obtained from the FHA-based equation, it is observed by the authors that the heavy load q value can be estimated by subtracting 0.02 from the light load q value for the worst case SCC design. Using the idea described earlier, a visual-assisted design method is proposed as follows.

Still considering the example in Fig. 7, output current curves with different q values are plotted using (11), and shown in Fig. 12. The solid line represents the output current of the highest resonant-frequency phase, which is the reference curve for the SCC compensations.

The first step is to try different q values in (11) and plot output current curves, and then identify the undercompensated curve that is the closest to the reference curve. Fig. 12 shows that when q = 0.83, the resultant output current curve is always below the reference curve, meaning that it is undercompensated; whereas the next curve (q = 0.82) intersects the reference curve, meaning that it is a critically compensated curve. Above two curves suggest that q = 0.83 ( $C_s$ -17%) is the undercompensated curve that is the closest to the reference curve. This result is in accordance with the observation made in Fig. 7.

Next, in order to guarantee sufficient SCC compensation at heavy load,  $q_{\min} = 0.81$ , which corresponds to series capaci-

Fig. 12. Visual assisted design method to find  $q_{\min}$ .

tance reduction of -19%, is chosen to be the worst case SCC design, which has additional 2% reduction of the series capacitance value based on the undercompensated curve. This result is also in accordance with Fig. 7. Fig. 12 also suggests that the heavy-load compensation curve intersects the reference curve at  $\omega_n = 0.71$  (or 164 kHz), which also agrees with the simulation results in Fig. 7.

Fig. 12 also provides the output current curve at q = 0.67 ( $C_s$ -33%), which is obtained by solving (12) directly. It is very far from the reference curve and it is very much overcompensated. This comparison demonstrates the accuracy advantage of the proposed visual-assisted design method.

Above steps derived the resonant capacitance variation range for worst case SCC design. The SCC capacitor value,  $C_a$ , is calculated in the next section.

## C. Design of Half-Wave SCC Capacitor Value

The half-wave SCC is in series with  $C_s$ , therefore the equivalent resonant capacitance is derived by substituting (5) into (2), given in the following equation:

$$C_{r} = \frac{2C_{a}C_{s}\pi}{2C_{a}\pi + 2C_{s}\pi - 2C_{s}\alpha + C_{s}\sin(2\alpha)}.$$

(13)

The control angle  $\alpha$  is from 0 to  $\pi$ , which modulates the resonant capacitance from  $C_r$ , min to  $C_r$ , max.  $C_r$ , max occurs at  $\alpha = \pi$ , which means the SCC MOSFET is always turned ON and the current always bypasses  $C_a$ . Therefore,  $C_r$ , max equals to  $C_s$ .  $C_r$ , min occurs at  $\alpha = 0$ , which means the SCC MOSFET is always turned OFF, and the current always flow through  $C_a$ . Therefore,  $C_r$ , min equals to  $C_s$  and  $C_a$  connected in series.

According to the discussion in the previous section,  $C_{r,\min}$  must be equal to or smaller than  $q_{\min}C_{s0}$  so that it is able to achieve load sharing in the worst case scenario. If  $C_{r,\min}$  is smaller than  $q_{\min}C_{s0}$ , the SCC is overdesigned: the  $C_a$  value will be smaller than necessary, and the  $C_a$  peak voltage will be higher, and thus the asymmetrical effect discussed in Section

III-B will be severer. For an optimal design of SCC,  $C_{r,\min}$  should equal to  $q_{\min}C_{s0}$ .

In the worst case scenario,  $C_s$  has the largest possible tolerance, thus  $C_s = C_{s0} \cdot c_{\max}$ . Substituting  $C_r = q_{\min}C_{s0}$ ,  $\alpha = 0$ , and  $C_s = C_{s0} \cdot c_{\max}$  into (13) gives

$$q_{\min}C_{s0} = \frac{C_a C_{s0} c_{\max}}{C_a + C_{s0} c_{\max}}.$$

(14)

Then solving (14) gives the expression of  $C_a$

$$C_{a0} = C_{s0} \frac{c_{\max} q_{\min}}{c_{\max} - q_{\min}}$$

(15)

where  $C_{a0}$  is the ideal value of  $C_a$ .

Considering that the  $C_a$  capacitor also has tolerance, the rated  $C_a$  capacitor value should be chosen such that its maximum possible value is still smaller than the designed  $C_{a0}$  value in (15). Therefore, the implemented  $C_a$  capacitor value should be selected according to the following equation:

$$C_{a,\text{rated}} \le \frac{C_{a0}}{e_{\text{max}}} \quad \text{where} \quad e = \frac{C_a}{C_{a,\text{rated}}} \quad (16)$$

where  $e_{\max}$  is the maximum ratio of actual  $C_a$  value and ideal  $C_a$  value due to the component tolerance.

## D. Design Procedure

The design procedure of the variable switching frequency half-wave SCC–LLC converter is summarized as follows:

- 1) Design the LLC power train parameters using existing methods. It is prudent to design the maximum output current higher than the specification. For example, if the required capacitance reduction to achieve load sharing is -20% (as will be obtained in Step 3), the designed maximum output current should be about 20% higher than the specification.

- 2) Identify the tolerances of the resonant components.

- 3) Visual-assisted design method: Use (11) to plot the output current curve of the highest resonant frequency phase (reference curve). Still use (11), but substitute the tolerance ratio c with the compensation value q, and plot the compensated output current curve of the lowest resonant frequency phase. Try different q values and visually identify the undercompensated curve that is the closest to the reference curve. Then subtracting a few percent (e.g., 0.02) from the undercompensated q value will give a good estimation of the heavy-load compensation q value,  $q_{\min}$ .

- 4) Use (15) and (16) to calculate the implemented  $C_a$  capacitor value.

#### V. EXPERIMENTAL RESULTS

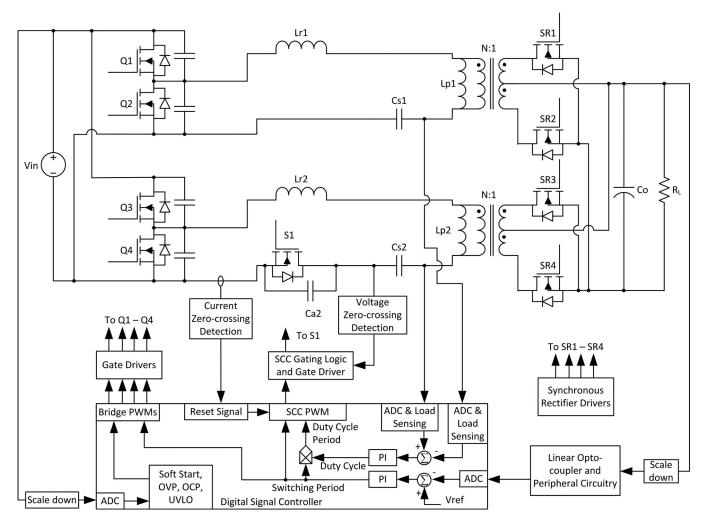

A 600-W two-phase interleaved variable switching frequency half-wave SCC–LLC converter is implemented to verify the feasibility and the advantages of the proposed control strategy. The system block diagram is shown in Fig. 13. The parameters are inTable I.

The resonant inductors are implemented with the transformers' leakage and are intentionally made nonidentical in order to test the load sharing performance. Because Phase 1's inductances are intentionally made smaller, its resonant frequency is higher than Phase 2; therefore, only Phase 2 needs a half-wave SCC to modulate the output current to match Phase 1. Two values of the SCC capacitor are tested in the circuit in order to show the effects of SCC overdesign. The gate driving signals of these two LLC converters operate at 90° phase shift for current ripple cancellation.

A Microchip DSC dsPIC33FJ32GS606 is used to implement the digital controller. A linear optocoupler is used to transmit output voltage signal to the primary side. The output voltage signal is sampled by an ADC, and then subtracted from a reference voltage value to create an error value. The error value is processed by a voltage-loop PI controller and becomes the switching period for both the half-bridge pulse-width modulation (PWM) and the SCC PWM. The phase shift between the two half-bridges is adjusted according to the switching period to maintain 90° phase shift. Two other ADCs are used to sample the resonant capacitor voltage, which reflects the output current level. The load sensing method can be adopted from either [41] or [42]. The load current error between the two phases is processed by a load-sharing PI controller and becomes the duty cycle of the SCC PWM. The SCC duty cycle is multiplied by the switching period and becomes the duty cycle period. The SCC PWM is synchronized with the zero-crossing points of the primary-side resonant current. The zero-crossing detection is implemented using a current transformer and a comparator. The synchronization is implemented using the DSC's external PWM reset function, which allows a logic signal from the current zero-crossing detection circuit to reset the digital PWM. An SCC gating logic circuit is used to turn ON the SCC MOSFET at the SCC voltage zero-crossing points, in order to eliminate the power loss in its body diode [43].

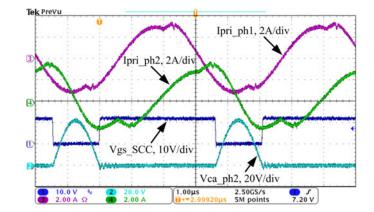

Fig. 14 shows the operation of the half-wave SCC. The SCC MOSFET is turned ON as soon as the SCC voltage returns to zero in order to prevent the MOSFET body diode from carrying current. The SCC MOSFET is always turned ON and OFF at ZVS condition, therefore the switching loss is negligible.

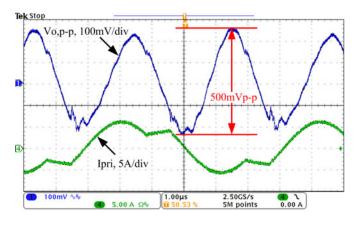

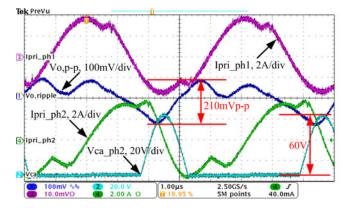

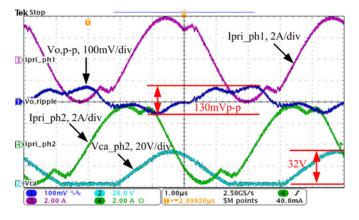

Figs. 15, 16, and 17 demonstrate the effectiveness of current ripple cancellation and load sharing. Small ripple indicates good load sharing performance. A separate 600-W single-phase LLC converter with the same input/output specification and output capacitance has been built for the purpose of comparison.

Fig. 15 shows waveforms of the single-phase LLC converter at 50-A load. The output voltage ripple is 500 mV peak to peak.

Fig. 16 shows waveforms of the SCC–LLC converter with the proposed control strategy at 50-A load. With the same output capacitance, the output voltage ripple is reduced to 210 mV peak to peak. From the resonant current waveforms, it can be seen that the output currents of the two phases are well balanced even though the resonant tanks are intentionally made different. This waveform is obtained when the  $C_a$  is 30 nF. It is noticeable that the resonant current of the two half-cycles in Phase 2 are slightly asymmetrical due to the half-wave SCC modulation.

Fig. 17 shows waveforms of the SCC–LLC converter with the proposed control strategy at 50-A load, with the SCC capacitance increased to 155 nF. It is observed that when  $C_a$  is larger,

Fig. 13. Implemented two-phase interleaved SCC-LLC converter with the proposed control strategy.

| I KOTOT ITE I AKAMETEKS |                                                     |

|-------------------------|-----------------------------------------------------|

| Switching frequency     | Variable around 200kHz                              |

| Input Voltage           | 400V nominal/300V minimum                           |

| Output Voltage          | 12V                                                 |

| Output Power            | 600W (300W × 2 phases)                              |

| Transformer Turns Ratio | 20:1, Center tapped                                 |

| Magnetizing Inductance  | 87µH(Phase1) 85µH(Phase2)                           |

| Resonant Inductance     | 12µH(Phase1) 14µH(Phase2)                           |

| Series Capacitors       | 36nF±5%                                             |

|                         | 30nF±3% (over-design case) or                       |

| SCC Capacitors          | 155nF±5% (optimal case)                             |

| Output Capacitance      | $1790\mu F (100\mu F \times 8 + 330\mu F \times 3)$ |

| Half-bridge MOSFET      | IPB60R190C6                                         |

| SCC MOSFET              | BSC060N10NS3G(100V,6mΩ)                             |

| SR MOSFET               | BSC011N03LS                                         |

TABLE I Prototype Parameters

the  $\alpha$  angle is smaller to achieve the same load sharing task. The SCC voltage amplitude is also significantly lower. As a result, the asymmetrical effect of the resonant current is mitigated, and is almost invisible. The output voltage ripple is further reduced to 130 mV peak to peak. As discussed in Section IV-C, for optimal performance, the  $C_a$  value should be as large as possible, but still sufficiently small to achieve load sharing in the worst case scenario.

Fig. 14. Operation of half-wave SCC.

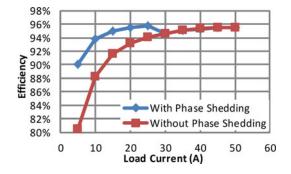

Fig. 18 shows the efficiency improvement using the phaseshedding technique in the proposed SCC–LLC converter. When the load current is below 50%, one phase is shut down. The 25 A (50%) load efficiency is improved from 94% to above 95.5%, and the 5 A (10%) load efficiency is improved from 81% to 90%.

Fig. 15. Output voltage ripple of single-phase LLC converter.  $I_o = 50$  A and  $C_o = 1790 \ \mu\text{F}.$

Fig. 16. Output voltage ripple of two-phase interleaved SCC–LLC converter with the proposed control strategy.  $I_o = 50 \text{ A}$ ,  $C_o = 1790 \mu$ F, and  $C_a = 30 \text{ nF}$ .

Fig. 17. Output voltage ripple of two-phase interleaved SCC–LLC converter with the proposed control strategy.  $I_o = 50 \text{ A}$ ,  $C_o = 1790 \,\mu\text{F}$ , and  $C_a = 155 \,\text{nF}$ .

### VI. CONCLUSION

A new control strategy is proposed for interleaved SCC–LLC converters. The switching frequency control is used for voltage regulation; thus, it can provide uncompromised peak gain range and frequency variation range compared to conventional LLC converters. The resonant frequency control is only responsible for load sharing, thus the half-wave SCC can be used to reduce cost and conduction loss. The load sharing characteristic of SCC–LLC converters is studied, and a visual-assisted design

Fig. 18. Efficiency comparison, with and without phase shedding.

method is proposed to determine the optimal SCC capacitance value. A 600-W two-phase interleaved SCC–LLC prototype is built and shows good performances of load sharing, current ripple cancellation, and light-load efficiency improvement.

#### REFERENCES

- B. Yang, F. C. Lee, A. J. Zhang, and G. Huang, "LLC resonant converter for front end DC/DC conversion," in *Proc. Appl. Power Electron. Conf. Expo.*, 2002, vol. 2, pp. 1108–1112.

- [2] Y. Zhang, D. Xu, M. Chen, Y. Han, and Z. Du, "LLC resonant converter for 48 V to 0.9 V VRM," in *Proc. Power Electron. Spec. Conf.*, 2004, vol. 3, pp. 1848–1854.

- [3] S. De Simone, C. Adragna, C. Spini, and G. Gattavari, "Design-oriented steady-state analysis of LLC resonant converters based on FHA," in *Proc. Int. Symp. Power Electron., Elect. Drives, Autom., Motion*, 2006, pp. 200– 207.

- [4] B. Lu, W. Liu, Y. Liang, F. C. Lee, and J. D. van Wyk, "Optimal design methodology for LLC resonant converter," in *Proc. Appl. Power Electron. Conf. Expo.*, 2006, p. 6.

- [5] B. Erkmen and I. Demirel, "A very low profile dual output LLC resonant converter for LCD/LED TV applications," *IEEE Trans. Power Electron.*, 2013, to be published.

- [6] B.-C. Kim, K.-B. Park, C.-E. Kim, B.-H. Lee, and G.-W. Moon, "LLC resonant converter with adaptive link-voltage variation for a high-powerdensity adapter," *IEEE Trans. Power Electron.*, vol. 25, no. 9, pp. 2248– 2252, Sep. 2010.

- [7] D.-Y. Kim, C.-E. Kim, and G.-W. Moon, "High-efficiency slim adapter with low-profile transformer structure," *IEEE Trans. Ind. Electron.*, vol. 59, no. 9, pp. 3445–3449, Sep. 2012.

- [8] M. G. L. Roes, J. L. Duarte, and M. A. M. Hendrix, "Disturbance observer-based control of a dual-output LLC converter for solid-state lighting applications," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 2018– 2027, Jul. 2011.

- [9] W. Feng, F. C. Lee, and P. Mattavelli, "Optimal trajectory control of LLC resonant converters for LED PWM dimming," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 979–987, Feb. 2014.

- [10] W. Feng, P. Mattavelli, and F. C. Lee, "Pulsewidth locked loop (PWLL) for automatic resonant frequency tracking in LLC DC–DC transformer (LLC–DCX)," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1862– 1869, Apr. 2013.

- [11] F. Musavi, M. Craciun, D. S. Gautam, W. Eberle, and W. G. Dunford, "An LLC resonant DC–DC converter for wide output voltage range battery charging applications," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5437–5445, Dec. 2013.

- [12] H. Hu, X. Fang, F. Chen, Z. J. Shen, and I. Batarseh, "A modified highefficiency LLC converter with two transformers for wide input-voltage range applications," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1946– 1960, Apr. 2013.

- [13] Q. Zhang, C. Hu, L. Chen, A. Amirahmadi, N. Kutkut, Z. J. Shen, and I. Batarseh, "A center point iteration MPPT method with application on the frequency-modulated LLC microinverter," *IEEE Trans. Power Electron.*, vol. 29, no. 3, pp. 1262–1274, Mar. 2014.

- [14] K. Jin and X. Ruan, "Hybrid full-bridge three-level LLC resonant converter—A novel DC–DC converter suitable for fuel-cell power

- [15] J.-Y. Lee, Y.-S. Jeong, and B.-M. Han, "An isolated DC/DC converter using high-frequency unregulated LLC resonant converter for fuel cell applications," *IEEE Trans. Ind. Electron.*, vol. 58, no. 7, pp. 2926–2934, Jul. 2011.

- [16] D. Dujic, C. Zhao, A. Mester, J. K. Steinke, M. Weiss, S. Lewdeni-Schmid, T. Chaudhuri, and P. Stefanutti, "Power electronic traction transformerlow voltage prototype," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5522–5534, Dec. 2013.

- [17] C. Zhao, D. Dujic, M. Akos, J. Steinke, M. Weiss, S. Lewdeni-Schmid, T. Chaudhuri, and P. Stefanutti, "Power electronic traction transformermedium voltage prototype," *IEEE Trans. Ind. Electron.*, 2013, to be published.

- [18] D. Dujic, G. K. Steinke, M. Bellini, M. Rahimo, L. Storasta, and J. K. Steinke, "Characterization of 6.5 kV IGBTs for high-power mediumfrequency soft-switched applications," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 906–919, Feb. 2014.

- [19] T. Jin and K. Smedley, "Multiphase LLC series resonant converter for microprocessor voltage regulation," in *Proc. Ind. Appl. Conf.*, 2006, pp. 2136–2143.

- [20] K.-H. Yi, B.-C. Kim, and G.-W. Moon, "A simple and novel two phase interleaved LLC series resonant converter employing a phase of the resonant capacitor," in *Proc. Energy Convers. Congr. Expo.*, 2009, pp. 754–757.

- [21] B.-R. Lin, W.-R. Yang, J.-J. Chen, C.-L. Huang, and M.-H. Yu, "Interleaved LLC series converter with output voltage doubler," in *Proc. Int. Power Electron. Conf.*, 2010, pp. 92–98.

- [22] M. Kim, "Two-phase interleaved LLC resonant converter with phase shedding control," in *Proc. Int. Power Electron. Conf.*, 2010, pp. 1642–1645.

- [23] H. Figge, T. Grote, N. Froehleke, J. Boecker, and P. Ide, "Paralleling of LLC resonant converters using frequency controlled current balancing," in *Proc. Power Electron. Spec. Conf.*, 2008, pp. 1080–1085.

- [24] B.-C. Kim, K.-B. Park, C.-E. Kim, and G.-W. Moon, "Load sharing characteristic of two-phase interleaved LLC resonant converter with parallel and series input structure," in *Proc. Energy Convers. Congr. Expo.*, 2009, pp. 750–753.

- [25] E. Orietti, P. Mattavelli, G. Spiazzi, C. Adragna, and G. Gattavari, "Current sharing in three-phase LLC interleaved resonant converter," in *Proc. Energy Convers. Congr. Expo.*, 2009, pp. 1145–1152.

- [26] E. Orietti, P. Mattavelli, G. Spiazzi, C. Adragna, and G. Gattavari, "Twophase interleaved LLC resonant converter with current-controlled inductor," in *Proc. Brazilian Power Electron. Conf.*, 2009, pp. 298–304.

- [27] Z. Hu, Y. Qiu, L. Wang, and Y.-F. Liu, "An interleaved LLC resonant converter operating at constant switching frequency," *IEEE Trans. Power Electron.*, 2013, to be published.

- [28] W.-J. Gu and K. Harada, "A new method to regulate resonant converters," *IEEE Trans. Power Electron.*, vol. 3, no. 4, pp. 430–439, Oct. 1988.

- [29] W. J. Gu and K. Harada, "A circuit model for the class E resonant DC–DC converter regulated at a fixed switching frequency," *IEEE Trans. Power Electron.*, vol. 7, no. 1, pp. 99–110, Jan. 1992.

- [30] J.-H. Cheng, A. F. Witulski, and J. L. Vollin, "Dynamic analysis of the Class-D converter at fixed frequency using amplitude and phase modulation," in *Proc. Power Electron. Spec. Conf.*, 1998, vol. 1, pp. 387–393.

- [31] J.-H. Cheng, A. F. Witulski, and J. L. Vollin, "A generalized DC model and low-frequency dynamic analysis for the Class-D converter at fixed frequency," *IEEE Trans. Power Electron.*, vol. 15, no. 6, pp. 1212–1220, Nov. 2000.

- [32] L. Huber and M. M. Jovanoviae, "Evaluation of AC VRM topologies for high-frequency power distribution systems," in *Proc. Appl. Power Electron. Conf. Expo.*, 2001, vol. 1, pp. 160–166.

- [33] Y.-T. Chen, W.-M. Lin, and Y.-H. Liu, "Analysis and design of a dimmable electronic ballast controlled by a switch-controlled capacitor," *IEEE Trans. Ind. Electron.*, vol. 52, no. 6, pp. 1564–1572, Dec. 2005.

- [34] H.-J. Chiu and S.-J. Cheng, "Single-stage voltage source charge-pump electronic ballast with switched-capacitor dimmer for multiple fluorescent lamps," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2915–2918, 2007.

- [35] D. Fu, B. Lu, and F. C. Lee, "1 MHz high efficiency LLC resonant converters with synchronous rectifier," in *Proc. Power Electron. Spec. Conf.*, 2007, pp. 2404–2410.

- [36] C. Adragna, S. De Simone, and C. Spini, "A design methodology for LLC resonant converters based on inspection of resonant tank currents," in *Proc. Appl. Power Electron. Conf. Expo.*, 2008, pp. 1361–1367.

- [37] X. Fang, H. Hu, Z. J. Shen, and I. Batarseh, "Operation mode analysis and peak gain approximation of the LLC resonant converter," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1985–1995, Apr. 2012.

- [38] X. Fang, H. Hu, F. Chen, U. Somani, E. Auadisian, J. Shen, and I. Batarseh, "Efficiency-oriented optimal design of the LLC resonant converter based on peak gain placement," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2285–2296, May 2013.

- [39] T. Liu, Z. Zhou, A. Xiong, J. Zeng, and J. Ying, "A novel precise design method for LLC series resonant converter," in *Proc. Int. Telecommun. Energy Conf.*, 2006, pp. 1–6.

- [40] G. Ivensky, S. Bronshtein, and A. Abramovitz, "Approximate analysis of resonant LLC DC–DC converter," *IEEE Trans. Power Electron.*, vol. 26, no. 11, pp. 3274–3284, Nov. 2011.

- [41] STMicroelectronics, "High-voltage resonant controller," L6599 datasheet, 2006.

- [42] Z. Hu, Y.-F. Liu, and P. C. Sen, "Cycle-by-cycle average input current sensing method for LLC resonant topologies," in *Proc. Energy Convers. Congr. Expo.*, 2013, pp. 167–174.

- [43] Z. Hu, Y. Qiu, and Y.-F. Liu, "Digital implementation of load sharing method for interleaved LLC converters," in *Proc. Control Modeling Power Electron.*, 2013, pp. 1–7.

**Zhiyuan Hu** (S'10) received the M.Sc. degree from the University of Ottawa, ON, Canada, in 2010. He is currently working toward the Ph.D. degree in electrical engineering at Queen's University, ON, Canada.

From 2007 to 2010, he was with Potentia Semiconductor Corp. and Power Integrations Inc. on power management ICs. His research interests include topology, control, and modeling of resonant converters, digital communication in isolated power supplies, and digital power factor correction. He has one U.S. patent pending and several inventions.

Mr. Hu received the Ontario Graduate Scholarship award in 2013, the Outstanding Presentation award at APEC'13, the Student Presentation Winner award at ECCE'13, and several conference travel awards from IAS-PELS and PSMA.

Yajie Qiu (S'13) received the M.Sc. degree from Anhui University of Technology, China, in 2011. He is currently working toward the Ph.D. degree in electrical engineering at Queen's University, ON, Canada.

His research interests include voltage regulators, resonant converters, and high-performance outdoor LED drivers.

Yan-Fei Liu (M'94–SM'97–F'13) received the Ph.D. degree from the Department of Electrical and Computer Engineering, Queen's University, Kingston, ON, Canada, in 1994.

From February 1994 to July 1999, he was with the Advanced Power System Division of Nortel Networks as a Technical Advisor. Since 1999, has been with Queen's University. Currently, he is a Professor in the Department of Electrical and Computer Engineering. His research interests include digital control technologies for high efficiency, fast dynamic

response dc-dc switching converter and ac-dc converter with power factor correction, resonant converters and server power supplies, and LED drivers.

Dr. Liu holds 22 U.S. patents and has published more than 130 technical papers in IEEE Transactions and conferences. He is also a principal contributor for two IEEE standards. He serves as an Editor of the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS OF POWER ELECTRONICS (IEEE JESTPE) since 2012, an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS since 2001, an Editor in Chief for special issue of Power Supply on Chip of IEEE TRANSACTIONS ON POWER ELECTRONICS from 2011 to 2013, as well as Technical Program Cochair for ECCE 2011. He has been serving as a Chair of PELS Technical Committee on Control and Modeling Core Technologies since 2013. He served as a Chair of PELS Technical Committee on Power Conversion Systems and Components from 2009 to 2012.

**Paresh C. Sen** (M'67–SM'74–F'89–LF'04) was born in Chittagong, Bangladesh. He received the B.Sc. (with Hons. in physics) and M.Sc. (Tech.) degrees in applied physics from the University of Calcutta, West Bengal, India, in 1958 and 1962, respectively, and the M.A.Sc. and Ph.D. degrees in electrical engineering from the University of Toronto, ON, Canada, in 1965 and 1967, respectively.

He is currently an Emeritus Professor of electrical and computer engineering at Queen's University, ON, Canada. He has worked for industries in India

and Canada and was a consultant to electrical industries in Canada. He has authored more than 215 technical papers in the general area of electric motor drives and power electronics. He is the author of two internationally acclaimed textbooks: *Principles of Electric Machines and Power Electronics* (Wiley 1989, 1997, 2013) and *Thyristor DC Drives* (Wiley 1981). He has taught electric machines, power electronics, and electric drive systems for more than 45 years. His research interests include power electronics, electric drive systems, switching power supplies, wind energy systems, digital control, and modern control techniques for power electronics and motor drive systems.

Dr. Sen has served IEEE in various capacities: as an Associate Editor, Distinguished Lecturer, Chairman of the technical committees on power electronics and energy systems, Session Organizer, Session Chairperson, and Paper Reviewer. He served as a Natural Science and Engineering Research Council of Canada Scientific Liaison Officer evaluating university-industry coordinated projects. He is globally recognized as an authority in power electronics and motor drive systems. He received the IEEE-IAS (Industry Application Society) Outstanding Achievement Award in 2008, and the IEEE-Canada Outstanding Engineering Educator Award in 2006 for his outstanding contributions over four decades as a Researcher, Supervisor, Teacher, Author, and Consultant. He received the IAS-IDC Prize Paper Award in 1986. He is a fellow the EIC. As an Emeritus Professor, he continues to be active in research, supervision of graduate students, and in several IEEE societies.